#### **Lecture Notes**

On

# Digital Electronics & Microprocessor

#### Handwritten

**Prepared By**

Sri Shailesh kumar Nayak

Lecturer in Electronics

### Number System

- A number system is simply a way to count.

- The most commonly used number systems are:-

- O Decimal number system

- (ii) Binary number system

- (ii) octal number system

- ( Hexadecimal number system.

# Base/Radix

The bare/readix of a number system is defined as the number of different digits

- A number Bystem with base on readex is will have is number of different digits from 0 → (12-1).

- The number system is represented by No. where N-Number b base on radix.

# Decimal Number System

- This System has base lo'.

- It has 10 distinct symbols (0,1,2,3,4,5,6,7,8,9)

- ex (498), + Hene 4 is the most significant digit (MSD) 4

8 is the least Significant digit (LSD)

# Binary Number System

- It has base 2.

- It has two base numbers o and 1. There, have numbers are called Bits.

- In binary number system, group of 4 bits is known as Nibble & group of Eight bits is known as Byte.

4 bits = 1 Nibble , 8 bits = 1 Byte

ex = 1011 | 1011 | MSB - MSB - MOST STANFICANT Bit

# Octal Number system

- It has a base of 8.

- It posses 8 distinct symbols (0,1,2,3,1,5,6,7)

# ex - (274)8

# Hexadecimal Number system

- The base for this System is 16

- This number system contains numeric digits (0,12,-...9) & alphabets (A,B,C,D,E&F) both 80 this is an Alphanumeric number System.

- Microphocesson deals with instructions is data that use hexadecimal number system for programming purpose.

- ex (A7)16, (9E3)H

## Conversion

# Decimal to Binary

ex converse (57) to Binary equivalent.

# Binary to Decimal

ex convert (10110)2 +0 Decimal equivalent.

- = 1×16 + 0×8+ 1×4 + 1×2+0×1

- = 16+0+4+2+0

- = 22

ex convert (13.125), to its binary equivalent.

ex convert (10111.101), to its decimal equivalent.

$$(10111\cdot101)_{2} = 1\times2^{4} + 0\times2^{3} + 1\times2^{2} + 1\times2^{1} + 1\times2^{\circ} + 1\times2^{-1} + 0\times2^{-2} + 1\times2^{-3}$$

$$= 1\times16 + 0 + 1\times4 + 1\times2 + 1\times1 + 1\times\frac{1}{2} + 0 + 1\times\frac{1}{8}$$

$$= 16 + 4 + 2 + 1 + 0.5 + 0.125$$

$$= 23.625$$

$$(10111\cdot101)_{2} = (23.625)_{10}$$

Decimal to octal

ex convert (259)10 to octal equivalent.

$$8 \frac{259}{8 32} - 3$$

$(403)_8$

octal to Decimal

ex convert (125) 8 to its decimal equivalent.

$$(125)_8 = 1 \times 8^2 + 2 \times 8^1 + 5 \times 8^6$$

=  $164 + 2 \times 6 + 5 \times 1$

=  $64 + 16 + 5$

=  $85$

# Decimal to Hexaderimal

ex convert (487), to its Hexadecimal equivalent.

# Hexadecimal to Decimal

e convert (286) to its decimal equivalent.

$$(2B6)_{16} = 2 \times 16^{2} + B \times 16^{1} + 6 \times 16^{6}$$

=  $2 \times 256 + 11 \times 16 + 6 \times 1$

=  $512 + 176 + 6$

### = 594

# Binary to octal

Note

- group 3 bit from LSB towards MSB.

- Add 'O' at the MSB which is short of J.

- write its octal equivalent.

| octal |

|-------|

| 0     |

| 1     |

| 2     |

| 3     |

| 4     |

| 5     |

| 6     |

| Ŧ     |

|       |

$$\frac{Ans}{(10110111)_2}$$

$\xrightarrow{Add 0}$   $010110111$   $267$

# Octal to Binany

- Represent 3 bit binary equivalent of Octal number individually.

ex convert (153) to its broany equivalent.

### Binary to Hexadecimal

- Combine 4 bit from LSB to MSB & add as many o to MSB as Short of 4.

- write its binary equivalent.

| Hexadecimal      |

|------------------|

| D                |

| V                |

| 2                |

| 3                |

| 4                |

|                  |

| 6                |

| 5<br>6<br>7<br>8 |

| 8                |

| 9                |

| Α                |

| В                |

| C                |

| D                |

| DE               |

| F                |

|                  |

ex convert (10111010110110), to its Hexadecimal equivalent.

# Hexadecimal to Brnany

- write 4 bit binary equivalent of Hexadecimal number individually.

ex convert (7BF)16 to its binary equivalent.

### octal to Hexadecimal

- convert octal to its binary equivalent.

- convert binary to its Hexa decimal equivalent

### Hexadecimal to octal

- convert Hexadecimal to its binary equivalent.

- convert binary to its octal equivalent.

ex convert (3754)8 to its Hexadecimal emivalent

```

Binary Addition

0 +0 = 0

0+1 = 1

1 +0 = 1

1 +1 = 10 or 0 with 1 carry.

Add (1011) 로 용 (1100)2

carry -> 05 1011

+ 1100

4 Add (101101) & (001110)2

00

101101

Binary Subtraction

0-0 = 0

0-1 = 1

1-0=1

```

$$0-0=0$$

$0-1=1$  (1 is bornowed & 0 becomes 10)

$1-0=1$

$1-1=0$

# Binary Division

ex Divide (11000), by (1000),

ex Divide (1111000)2 by (100)2

| Binany  | Decimal |

|---------|---------|

| 0       | 0       |

| 1       | 1       |

| 10      | 2       |

| 1.1     | 3       |

| 100     | 4       |

| 101     | 5       |

| 110     | 6       |

| 1.1.1   | 7       |

| 1000    | 8       |

| 1001    | 9       |

| 1010    | 10      |

| 1011    | 1.1     |

| 1100    | 12      |

| 1101    | 13      |

| 1110    | 14      |

| 1 1 1 1 | 15      |

# 1's Complement

- 1's complement of a binary number is obtained by changing 0 to 1 & 1 to 0.

- The complemented value represents the negative of the original number.

- Find i's complement representation of 101101

101101

010010 1's complement

# 2's Complement

- Find 1's complement, then add 1 to the 1's complement.

& Find 1's complement of 1010.

$$1^{3}$$

complement  $\rightarrow 0101$

$+ 1$

$2^{3}$  complement  $\rightarrow 0110$

ex Find 2's complement of 101101.

Note

- A negative number can be converted into a positive number by finding its 2's complement.

- The MSB on the left most bit indicales the gign. If it is 'I the number is negative & if 'o' the number is positive.

ex Represent -6 in 2's complement form.

Browning equivalent of  $6 \rightarrow 00000110$ 1's complement  $\rightarrow 11111001$  + 1 1111010

10

# Subtraction in 2's complement method

- Ignone if canny occur.

- If MSB of result is I then it is a negative number & If MSB it o then it is a positive number.

- 2's complement of nesult gives the original number if regult is negative.

ex Subtract & from 9 wing 2's complement in 8-bit.

9 -> 00001001

Brany of 8 - 00001000

1's complement -> 11110171

215 complement + 11111000

Brany 4 9 - 0000 1001

2'5 complement of 8 -> + 11111000

(1970 Te) MSB > 0

tue number

result -> (00000001) i.e (1),0

ex subtract 18 from 13 using 235 complement 13-18= 2

Binary of 18 - 00010010

1's Complement -) 11101101

2 15 cumplement 11101110

Brany of 13 -) 00001101

215 complement of 18 +11101110

10111011

MSB -) I i.e negative number

```

regul -> 11111011

1/5 complement -) 00000100

00000101

o's complement +

(00000101), = (5)10

i.e result is '-5'.

Add -15 & -20

Binary of 15 - 00001111

1)s complement -> 11110000

1111 0001

215 complement 7

Binany of 20 -) 00010100

1's complement + 11101011

215 complement -> TITOITOO

00

2's complement of 15 i.e. - 15 7

11110001

" 20 i-e-20 -> + 11 101 100

11

10111011 (D.

Carry

```

(Ignore)

MSB+1 i.e Negative

result  $\rightarrow |1011101|$ 1's complement  $\rightarrow 00100010$ + 1

2's complement  $\rightarrow 00100011$ (00100011)<sub>2</sub> = (35)<sub>10</sub>

i.e result is -35'

# weighted Binary codes

In weighted codes, for each position, there is specific weight attached

# Binary Coded Decimal CBCD

- In this code, each digit of a decimal number is represented by binary equivalent.

- It is a 4-bit binarry code.

- It is also known as '8-4-2-1 code' on simply 'BCD code'.

- It is a weighted code system.

- ex express (943)10 in BCD or 8421 code.

(100101000011) BCD

| BCD (8421) | Binary | Decimal |

|------------|--------|---------|

| 0000       | 0000   | 0       |

| 0001       | 0001   | 1       |

| 0010       | 0010   | 2       |

| 0011       | 0011   | 3       |

| 0100       | 0100   | 4       |

| 0101       | 0101   | 5       |

| 0110       | 0110   | 6       |

| 0111       | 0111   | 7       |

| 1000       | 1000   | 8       |

| 1001       | 1001   | 9       |

| 00010000   | 1010   | 10      |

| 00010001   | 1011   | 1. 1    |

| 00010010   | 1100   | 12      |

| 00010011   | 1101   | 13      |

| 00010100   | 1 / 10 | 14      |

| 00010101   | 1111   | 15      |

Express (214.83) to its BCD equivalent.

174

### Non-weighted wodes

In non-weighted code, there is no positional weighted. i-e- each position within the binary number is not assigned a prefixed value.

### Excess-3 code

In excess-3 (XS-3) code three (3) is added to cach decimal digit before converting it into equivalent binary.

- Each 4 bit group in excess-3 code is equal to a specific decimal digit.

| Desimal | Excess-3 code | Binary  |

|---------|---------------|---------|

| 0       | 0011          | 0000    |

| 1       | 0100          | 0001    |

| 2.      | 0101          | 0010    |

| 3       | 0110          | 0011    |

| 4       | 0111          | 0100    |

| 5       | 1000          | 0101    |

| 6       | 1001          | 0110    |

| 7       | 1010          | 0111    |

| 8       | 1011          | 1000    |

| 9       | 1100          | 1001    |

| 10      | 01000011      | 1010    |

| 1.1     | 01000100      | 1011    |

| 12      | 01000101      | 1100    |

| 13      | 01000110      | 1101    |

| 14      | 01000111      | 1110    |

| 15      | 1 01001000 1  | 1 1 1 1 |

Express 129 to an excess-3 numbers.

# Greay codes

| Decimal | Brnany  | Gray codes |

|---------|---------|------------|

| 0       | 0000    | 0000       |

| 1       | 0001    | 0001       |

| 2       | 0010    | 0011       |

| 3       | 0011    | 0010       |

| 4       | 0100    | 0110       |

| 5       | 0101    | - 0111     |

| 6       | 0110    | 0101       |

| 7       | 0111    | 0100       |

| 8       | 1000    | (100       |

| 9       | 1001    | 1101       |

| 10      | 1010    | 1111       |

| 1.1     | 1011    | . 1110     |

| 12      | 1100    | 1010       |

| 13      | 1101    | 1011       |

| 14      | -1110   | 1001       |

| 15      | 1 1 1 1 | 1000       |

# Binary to Gray Conversion

- MSB in the gray code is same as corresponding digit in binary number.

- Standing from 'left to Right', add each adjacent pairs of binary bits to get next gray code bit, discarding the Carry.

ex convert (10010)2 to gray code.

# Carray to Binary Conversion

- MSB of Binary is same as that of gray code.

- Add each binary bit to the gray code bit of the next adjacent position to get next bit of the binary number, discarding the carry.

convert (11011) Gray to Binary code.

ex Convert (1001 1011) array to Binary code.

### Eneon Detecting code

- . In digital systems a world consisting of group of bits is stored as a unit & moves from one unit to another.

- · when this world it transmitted from one memory Locatron to another on to an anithmetic unit, an error may occur.

- If a task of performing addition of 01001101& 11000111 is required & when the device thousand these words from memory, it may possible that error in 3rd bit of first world can occur as 01101101. This will result in an error in the addition.

- For detecting such ennors, a method called 'Parity' is used.

# Parity

- For detecting such errors, an additional bit known at parrity bit is added with the numbers.

- For odd parity, this parity bit is set to 1 so that the sum of bits in the number is odd.

- For even parity, the adding of the parity bit to the group of bits produce an even number of 1's.

| Decimal | BCO code | even parity | odd parity |

|---------|----------|-------------|------------|

| 0       | 0000     | 0           | 1          |

| 1       | 0001     | 1           | 0          |

| 2       | 0010     | ١           | 0          |

| 3       | 0011     | 0           | 1          |

| 4       | 0100     | 1           | D          |

| 5       | 0101     | υ           | ,          |

| 6       | 0110     | 0           | 1          |

| 7       | 0111     | t           | 0          |

| 8 -     | 1000     | 1           | 0          |

| 9       | 1.001    | O           | 1          |

|         |          |             |            |

|         |          |             |            |

# Logic Gales

Basic Chaler Special purpose Grave Universal Gate EX-OR (XOR) TOM MAND EX-NOR (XNOR) NOR AND OR

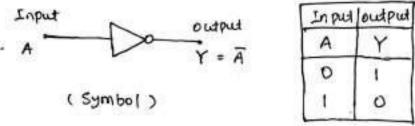

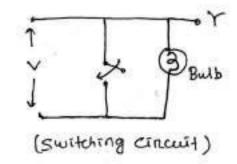

### NOT Gate

- The NOT gate has a single input vaniable and a single output variable.

- The NOT operation is also referred to as 'Inversion' or COMPLEMENTATION' .

- Thus its output logic level is always opposite to the logic level of its input.

- For input A, [Y = A]

| 1 | in pus | ouspus | ŀ |

|---|--------|--------|---|

|   | A      | Y      |   |

|   | 0      | 1      |   |

|   | 1      | 0      |   |

|   |        |        |   |

(Trush Table)

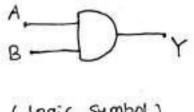

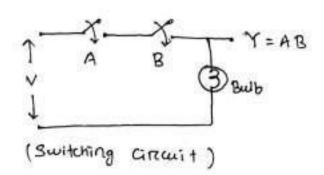

#### AND Crate

- The AND gate can have two ore more inputs but only one output.

- If all the inputs on any of the input is 'o' the output is o'. The output is '1' only when all the inputs are 1'.

| ( | Logic | sy mbol | ) |

|---|-------|---------|---|

|   |       |         |   |

| Inf | rut | output |

|-----|-----|--------|

| A   | В   | Y      |

| 0   | 0   | 0      |

| 0   | 1   | 0      |

| 1   | 0   | 0      |

| 1   | 1   | 1 1    |

( Irust Table)

- The logical expression is Y = AB

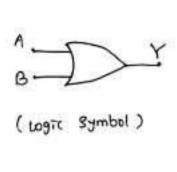

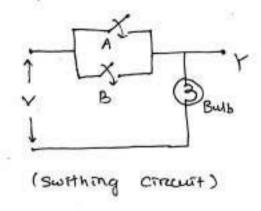

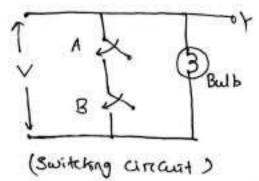

#### OR nate

- . The OR gate can have two on more inputs but only one output

- If all the inputs on any of the input is '1' the output it ligh OR'1'.

If all the inputs are low or 'o' then output is 'o'.

| 10 | pul | output |

|----|-----|--------|

| Α  | В   | Y      |

| 0  | 0   | 0      |

| 0  | 1   | 1      |

| 1  | 0   | 1      |

| 1  | 1   | 1      |

(Truth Table)

- The Logical expression is [Y = A+B]

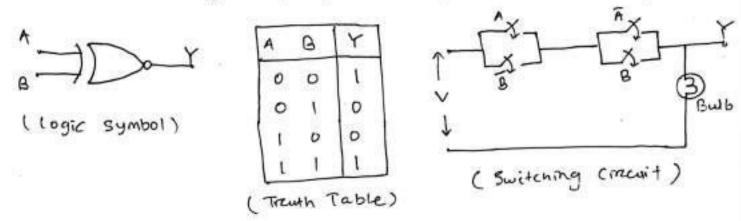

#### NAND Grate

- It may have two or more inputs but only one output.

- The NAND Gate is a AND Gate followed by NOT Gate. It is a NOT-AND operation

- The output is I when either one of the input on when both the inputs are at logic o'

- The NAND gate output is exactly inverse of the AND gate.

(Truth Table)

A DON'Y

B (Waic Symbol)

| A | B | Y  |

|---|---|----|

| 0 | 0 | 1  |

| 0 | U | 11 |

| 1 | 0 | 1  |

| 1 | 1 | 0  |

- The logical expression is Y = A·B

#### NOR Grate

- It may have two or more input and an output.

- . A NOR gade is a combination of or gate & NOT Gate. It is a NOT-OR operation.

- The output is '1' only if all the inputs are at logic 'o'.

( Logic Symbol)

| A | 13 | Y |

|---|----|---|

| 0 | 0  | 1 |

| 0 | 1  | 0 |

| 1 | 0  | 0 |

| 1 | 1  | 0 |

| 38 | 3 | 3) | Bull    |

|----|---|----|---------|

|    |   | -  | KUNT    |

|    | 1 |    |         |

|    |   |    |         |

|    | - |    | circuit |

- The logical expression is Y = A+B

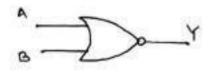

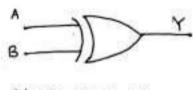

# EX-OR Gate

- It is a two input single output logic gate.

- output is high on's only when only one of its inputs is high(1).

- It is also known as 'stain case switch'.

( logic symbol )

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| l | 0 | 1 |

| 1 | 1 | 0 |

- Lugical Expression is Y = A + B

- ABB = AB + AB

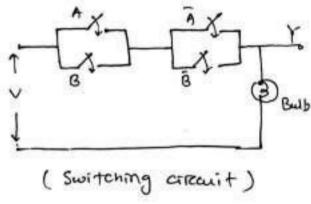

# EXNOR hate

- It is a two input and one output logic circuit.

- output is '1' only when both the inputs are same.

- It is also called gate of equivalence or 'coincidence logic'.

- AOB = A.B + A.B

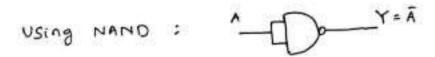

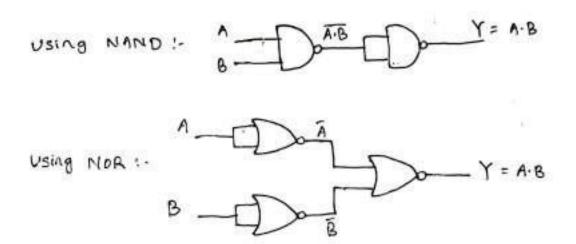

Realization of Logic gates using universal gate CNAND, NOR)

### Not gate realization

### AND gate realization

Cal

# OR gate realization

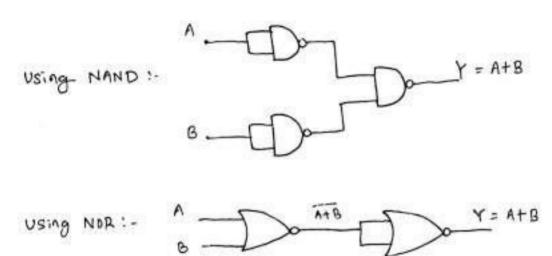

ex Realize AB+CD using logic gates.

### Boolean Algebra

- The binary operations performed by any digital circuit with the set of elements 0 & 1, are called logical operations or logic functions.

- The algebra used to symbolically represent the logic function is Called Boolean algebra.

- Boolean algebra is a system of mathematic lugic for the analysis & designing of digital System.

#### AND operation

A . A = A

A . 0 = 0

A . 1 = A

A . A = 0

#### of operation

A + A = A

Ato = A

A + 1 = 1

A+ A = 1

#### NOT Operation

$$\overline{A} = A$$

$\overline{T} = 0$   $\overline{O} = 1$

#### Laws of Boolean Algebra

#### Commutative Laws

- 1 A+B = B+A

- (i) A-B = B-A

## Associative Laws

- ( (A+B) + C = A + (B+C)

- (1) (A.B). ( = A.CB.C)

# Distributive Laws

- ( ACB+c) = AB+AC

- (1) A + BC = (A+B) (A+C)

# Idempotence Law

- 1 A. A = A

- (i) A + A = A

#### Absorption Law

- ( A + AB = A (1+B) = A

- (1) A(A+B) = A

#### Involutionary law

#### De Morigan's Theorem

The complement of the product of variables is equal to the sum of their individual complements.

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

(i) The complement of a sum of variables is equal to the product of their individual complements.

Transposition Theorem

Proof RHS = (A+C)(A+B)

- = O + ÁC + AB + BC (A+Ã)

- = AB+ ABC + AC+ACB

- : AB(I+C) + AC(I+B)

- = AB + AC = LHS

## Proof of Demoisgan's Law

| Α | B | Ā | B | A-R | A·B | A+B | A+B | A+B | A.B |

|---|---|---|---|-----|-----|-----|-----|-----|-----|

| 0 | 0 | 1 | 1 | 0   | 1   | 1   | 0   | 1   | 0   |

| 0 | ţ | 1 | 0 | 0   | t   | 1   | 1 1 | 0   | 0   |

| 1 | 0 | 0 | 1 | 0   | 1   | 1   | 1   | 0   | -   |

| 1 | 1 | 0 | 0 | 1   | 0   | 0   | 1   | 10  | 0   |

# Simplification of logic expression using Boolean algebra:

$$= xY + xY + 0 \qquad (x \cdot X = X, Y \cdot Y = Y, Y \cdot \overline{Y} = 0)$$

$$= XY \qquad (XY + XY = XY)$$

$$= A \cdot I + \overline{A} \cdot I \qquad (B + \overline{B} = I)$$

= 1

```

( P + Paa + a+R

= P+PaR + Q.R

= P + R (Pa+ a)

= P + P (P+@)(Q+@)

= p + \bar{p} (\bar{p} + \bar{a}) \cdot 1 \qquad (\alpha + \bar{a} = 1)

= P+ P. (P+Q)

. P + PR + PR

= (P+P)(P+P) + Pia

= P+ R + RQ

(P+ P=1)

= P + P(1+a)

= P+P

O XT + XYZ + × LY+×·F)

= \overline{X(\overline{Y}+YZ)} + X(Y+X)(Y+\overline{Y})

= \overline{x(r+r)(r+z)} + x(r+x) (Y+ \overline{r} = 1)

X ( T+z) + XY + XX

XT +XZ + XY +X

(A+B = A·B => De Moregan's law)

X.F. XZ + X(Y+1)

(\overline{x} + \overline{\overline{y}})(\overline{x} + \overline{z}) + x

= X.x+x.z+x.++=++

= x + x. 2 + x. Y + 2Y + x

x (1+2+Y) + x + 2Y

= x +x+2Y

= 1+ 2Y

( I = X + X )

(1+A=1 ⇒ or operation)

```

#### Canonical form

All the terms contain all the variables either in complementary or in uncomplementary form.

of f(A,B,C) = ABC + ABC + ABC

#### Minterm

mintered is a product term, it contains all the variables either Complementary or uncomplementary form for that combination the function output must be '1'.

- In minterems we assign '1' to each uncomplemented variable & 'o' to each complemented variable.

#### maxterem

maxterm is a sum term, it contains all the varziables either complementary or uncomplementary form for that combination the function output must be 0.

- In maxterims we assign o' to each uncomplemented variable & 1 to each complemented variable.

| Α | В | C | minterm  | Maxterin       |

|---|---|---|----------|----------------|

| 0 | 0 | 0 | mo = TBE | Mo = A + B + C |

| 0 | 0 | 3 | m, = ABC | M, = A+B+E     |

| 0 | t | 0 | mi = ABC | M2 = A+B+C     |

| 0 | 1 | 1 | m3 = ABC | M3 = A+B+C     |

| 1 | 0 | 0 | ma = ABC | M4 = T+B+C     |

| i | 0 | 1 | ms = ABC | M5 = A+B+C     |

| ì | 1 | 0 | me = ABE | M6 = A+B+C     |

| 1 | 1 | 1 | my = ABC | Mq = A+B+E     |

# Sum of Product form (SOP)

- The SOP expression usually takes the form of two or more variables ANDed together.

- SOP forms are used to write logical expression for the output becoming logic 1'.

Notation: P(A,B,C) = Em(3,5,6,7) $Y = m_3 + m_5 + m_6 + m_7$

Y = ABC + ABC + ABC + ABC

# Preoduct of sum form (POS)

- The POS expression usually takes the form of two or morce ored variables within parentheses, ANDED with two or morce such terms.

- POS forems are used to write logical expression for output becoming logic 'o'.

Motalion :-

$f(A,B,C) = \pi M(O,1,2,4)$   $Y = M_0 \times M_1 \times M_2 \times M_3$ Y = (A+B+C)(A+B+C)(A+B+C)(A+B+C)

# Standard Sum of product form

- It is also called canonical sop forem.

ex Y = A + BC . Represent in cononical form

Y = A + BC = A (B+B)(C+Z) + BE (A+A)

= ABC + ABE + ABC + ABE + ABE + ABE

= ABC + ABC + ABC + ABC + ABC

### Standard product of sum form

- It is also called canonical POS form.

ex Represent Y=(B+E)(A+B) in canonical form

Y = (B+2+AA) (A+B+C2)

= (A+B+E)(A+B+E)(A+B+E)(A+B+E)

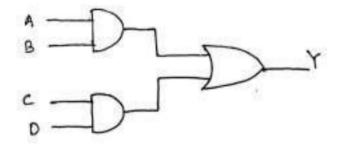

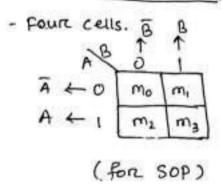

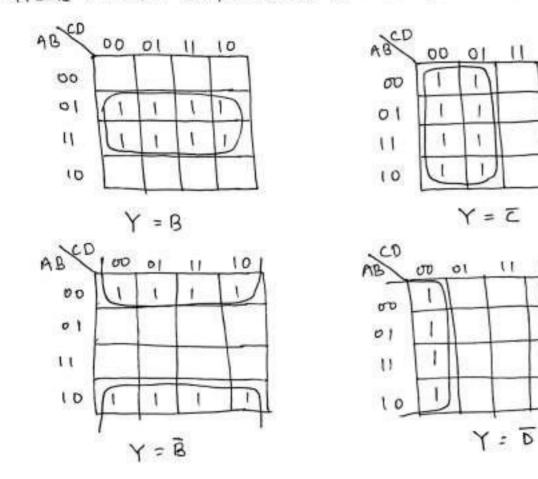

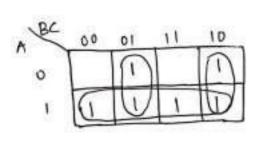

# Karenaugh Map (K-Map)

The karenaugh map is a graphical method which provides a systematic method fore simplifying the Bookean expressions

- In this technique, the information contained in a truth table on available in sop or pos form is represented on k-map.

- In n-variable k-map there are 2" cells.

- critical code has been used for the identification of cells.

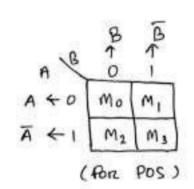

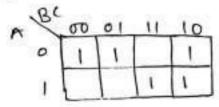

### Two variable k-map

## Three variable k-map

| V &   | 8+C | 8+Z | 1<br>1 | B+C |

|-------|-----|-----|--------|-----|

| A + 0 | Mo  | M,  | M3     | M2  |

| A+1   | Ma  | M5  | Ma     | ME  |

|       | (F  | on  | POS    | )   |

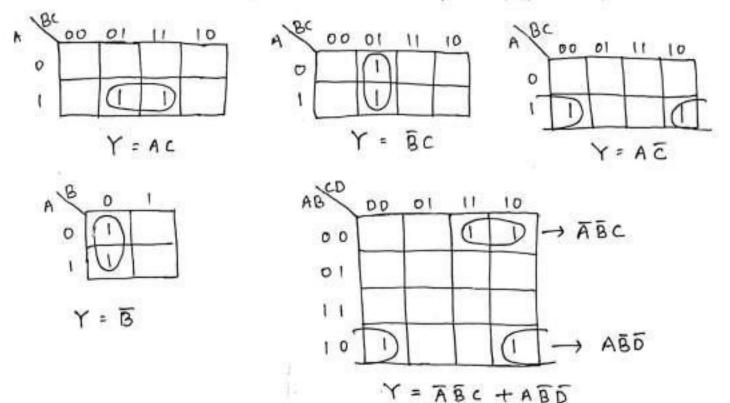

## Four variable K-map

| Sixteen cells | 7   | ZD<br>T        | CO              | ¢ ↑ |

|---------------|-----|----------------|-----------------|-----|

| ÃĒ ← DO       | 00  | m <sub>1</sub> | m 1             | 10  |

| 9000-EV. 8    | mo  |                | m <sub>3</sub>  | 12  |

| AB ← 01       | mq  | m <sub>5</sub> | m <sub>3</sub>  | m/6 |

| AB + 11       | m12 | MIS            | m <sub>15</sub> | m14 |

| AB €10        | mg  | mq             | m) 11           | mio |

|     | 48 0        | C+D | C+D<br>1 | C+D<br>↑       | 7   |

|-----|-------------|-----|----------|----------------|-----|

| A+B | ←00         | Mo  | Mi       | M <sub>3</sub> | M2  |

| A+B | -01         | MA  | Ms       | Ma             | Mb  |

| ā+ā | <b>←</b> 11 | Min | MI3      | MIS            | Min |

| Ā+B | 410         | Me  | Ma       | M"             | MID |

# Simplification of logical functions using k-map

Simplification of Logical functions with k-map is based on the Preinciple us combining terms in adjacent cells.

### Looping

- The expression for output Y can be simplified by properly combining those cells in the k-map which contains '1's for sop on O's for pos. The process of combining these 1's on b's is called looping.

- Chroups are made up of 2,4,8,16 & So on.

- · By folding K-map over its edges, the number of i's or o's overlapping forms the group.

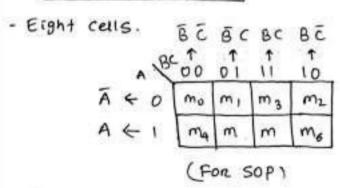

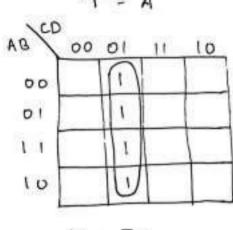

# looping groups of two (pairs)

Looping a pair of adjacent 1's in a k-map eliminates the variable that appears in complemented & uncomplemented form.

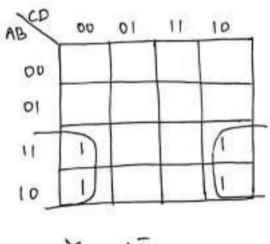

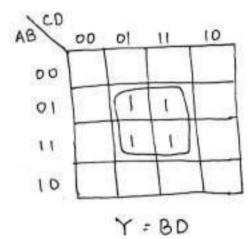

# Looping groups of four (Quads)

Looping a quad of 1's eliminates those two variables that appears in both complemented & uncomplemented form.

Y = AD

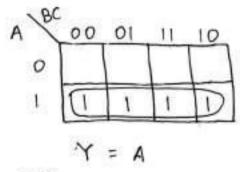

# Looping groups of eight (octets)

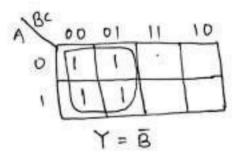

copping an octet of 1's eliminates those three variables that appear in both complemented & uncomplemented form.

# simplification rewer

- construct the K-map & place 1's in those cells corresponding to the 1's in the truth table.

- Examine the map for adjacent 1's & loop those 1's which are not adjacent to any other 1's.

- Look for those 1's which are adjacent to only one other 1 . Loop any pair containing such a 1 .

- Loop any octet even it contains some 1's that have alreedy been looped.

- loop any quad that contains one or more 115 which have not already been looped, making sure to use the minimum no. of loops.

- loop any pairs necessary to include any 1's that have not yet been looped, making sure to use the minimum numbers of Loops.

- 5 Form the OR sum of all the terms generated by each loop.

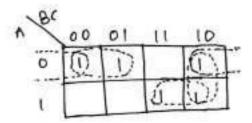

# **Emplicant**

Implicant is a product term on the given function, for that combination the function output must be 1.

### Prime Implicant (PI)

Preime implicant is a smallest possible product term on the given function, removing any one of the literal from which is not possible.

# Essential Praime Implicant (EPI)

Essential preime implicant is a preime implicant, it must cover atleast one minterm, which is not covered by any other prime implicant.

For the given K-map. Pind implicant, prime implicant & Essential Prime implicant.

AMS

Implicant = total no. cf 1 = 5

Implicant = ABC, ABC, ABC, ABC, ABC

Prime Implicant = AB, AC, AB, BE

Essential Prime Implirant = AB, AB

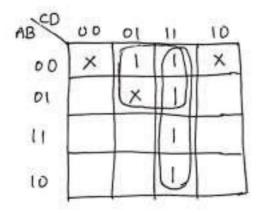

### Don't care condition

- Some logic circuits can be designed so that there are centain input combinations for which there are no specified output levels, usually because these input combinations will never occur.

- So a circuit designer is free to make the output for any 'don't care' condition either a 'o' on '1' in order to produce the simplest output expression.

- It is denoted as 'd' or 'x'.

- mapping of don't care is not compulsory.

- Solve the following

- ① In terms of SOP & don't care conditions.

P(A,B,C,D) = Em(1,3,7,11,15) + d(0,2,5)

- (i) In terms of POS & don't care conditions \$(A,B,C,D) = MMC4,5,6,7,8,12).d(1,2,3,9,11,14)

#### Bolution

@ f(A,B,(,D) = &m(1,3,7,11,15) + d(0,2,5)

| ABO | σĐ | 01 | ŭ | 10 |   |

|-----|----|----|---|----|---|

| 00  |    | d  | d | 어  |   |

| 01  | 0  | 0  | 0 | 0  |   |

| 11  | 10 | 1  |   | d  | 1 |

| (0) | 0  | d  | d |    | 1 |

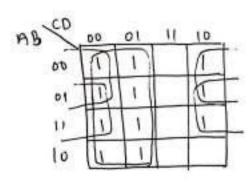

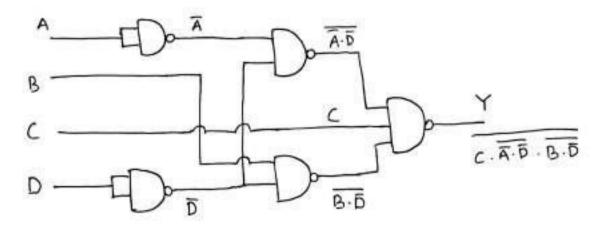

By solve the following function using K-map & realise the reduced function using (i) NAND gates (ii) NOR gates

For NAND gate realization, we we  $\overline{A} = A$   $Y = \overline{\overline{C} + A\overline{D} + B\overline{D}}$

$$= \overline{\overline{C} \cdot \overline{A \cdot \overline{D}} \cdot \overline{B \cdot \overline{D}}}$$

$$= \overline{C \cdot \overline{A \cdot \overline{D}} \cdot \overline{B \cdot \overline{D}}}$$

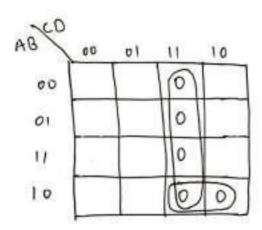

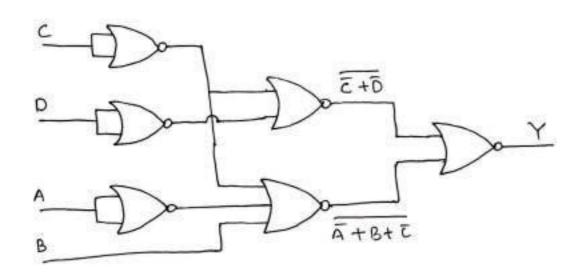

$$Y = (\overline{C} + \overline{D}) \cdot (\overline{A} + B + \overline{C})$$

$$= (\overline{C} + \overline{D}) \cdot (\overline{A} + B + \overline{C})$$

$$= (\overline{C} + \overline{D}) + (\overline{A} + B + \overline{C})$$

& Simplify the Boolean function, F = Em (1, 2, 4, 5, 6,7).

901°

# Combinational Logic concuit

- A combinational circuit consists of an interconnection of logic gates, whose outputs at any instant of time are determined from Present combination of inputs only.

- The combinational circuit do not we any memory. The previous state of input does not have any effect on the present state of the circuit.

- The combinational circuit can have an 'n' number of inputs and 'm' number of outputs.

#### combinational crizalit design

- @ Identify number of inputs &outputs.

- (1) Construct treath table.

- (ii) Wreite output logical expression.

- ( minimize logical expression.

- 1 Implement logic circuit.

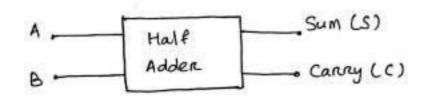

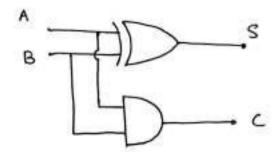

#### Half Adder

- The half adder is an arithmetic circuit used to perform the addition of two single bits.

- Two input variables to the half adder designate the augend & addend bits and the Output variables produce the sum & carry.

A, B → Input S, C → Output

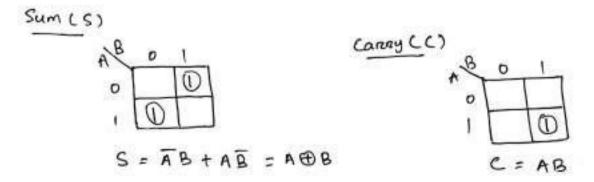

# Treuth Table

| Jub | uts | Ou | t puts |

|-----|-----|----|--------|

| A   | В   | 5  | د      |

| 0   | 0   | 0  | 0      |

| 0   | 1   | 1  | 0      |

| 1   | 0   | 1  | D      |

| 1   | 1   | 0  | 1      |

The logical expression for S&C is obtained using K-map.

logic diagnam

Half Adden using NAND gates only :-

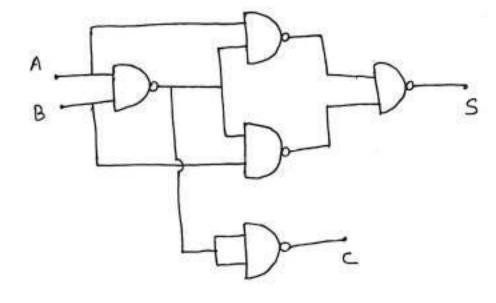

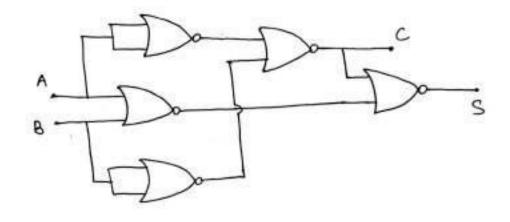

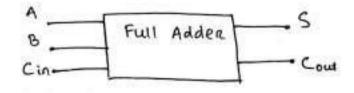

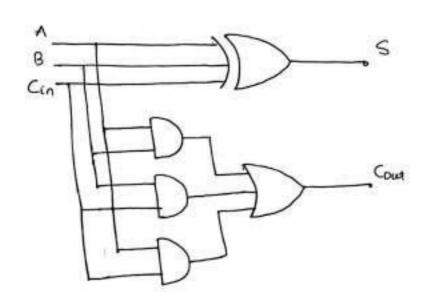

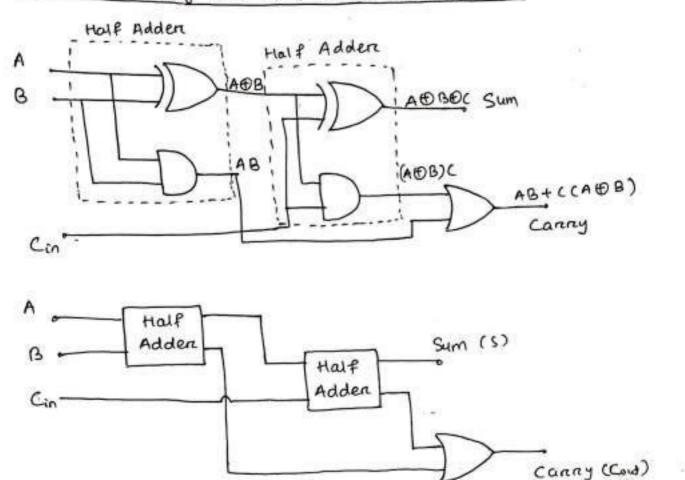

#### Full Adder

- A Full adder is a combinational circuit that periforms the arithmetic Sum of three input bits. It consists of three input variables designated by augend, addend & the carry bit. The two output variables produce the sum & carry.

- The third input c represents the carry from the previous lower significant position.

#### Truth Table

| In | put s | :   | owt | out  |

|----|-------|-----|-----|------|

| A  | B     | Cin | S   | Cout |

| 0  | 0     | 0   | 0   | O    |

| 0  | 0     | 1   | 1   | 0    |

| O  | 1     | 0   | 1   | 0    |

| 0  | ١     | 1   | 0   | ı    |

| V  | 0     | 0   | 1   | 0    |

| 1  | 0     | - 1 | D   | t    |

| 1  | - 1   | 0   | 0   | ١    |

| 1  | 1     | 1   | 11  | 1    |

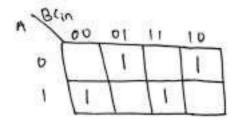

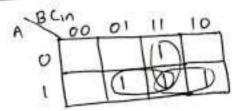

# Sum (S)

### Canny (Cout)

Cous = A Cint AB + BCin

= ABBECW

### wgic diagram

# carry (Cous)

$$cow = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$$

$$= \overline{C(AB + \overline{AB})} + \overline{AB(CC + C)}$$

$$= \overline{C(ABB)} + \overline{AB}$$

# Full Adder using two Half adders & an OR-gate

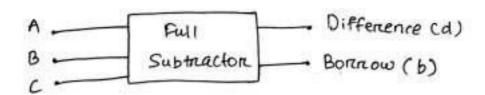

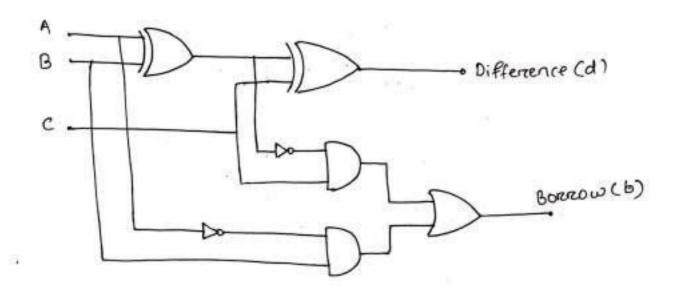

### Full Subtractor

- · A full Subtractor is an arithmetic circuit which performs a Subtraction between two bits taking into account that a 'I' may have been borrowed by a lower significant stage.

- A full Subtractor has three inputs of two outputs.

# Treuth Table

| 1, | put |   | out | put |

|----|-----|---|-----|-----|

| A  | B   | C | d   | b   |

| 0  | 0   | 0 | 0   | 0   |

| 0  | 0   | 1 | 1   | 1   |

| 0  | Ţ   | 0 | 1   | 1   |

| 0  | 1   | 1 | 0   | 1   |

| 1  | 0   | 0 | 1   | 0   |

| 1  | 0   | 1 | 0   | 0   |

| 1  | 1   | 0 | 0   | 0   |

| 1  | 1   | 1 | 11  | 1   |

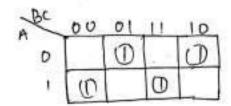

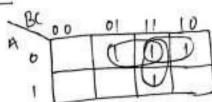

#### Difference (d)

# Borrow (b)

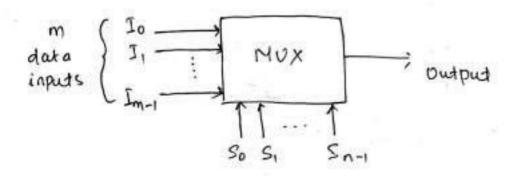

# Multiplexen (MUX)

- It is a combinational circuit that selects binary information from one of many input lines and directs it to single output line.

- The selection of a panticular input line is controlled by a set of selectron lines.

- There are 2" input imes & n selection lines.

- Multiplexer is also known as Data Selector, many to one crecuit, universal logic converter, parallel to serial converter.

$M \rightarrow Total no. uf data input in <math>A \rightarrow Number of Selection lines$

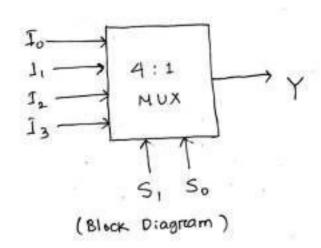

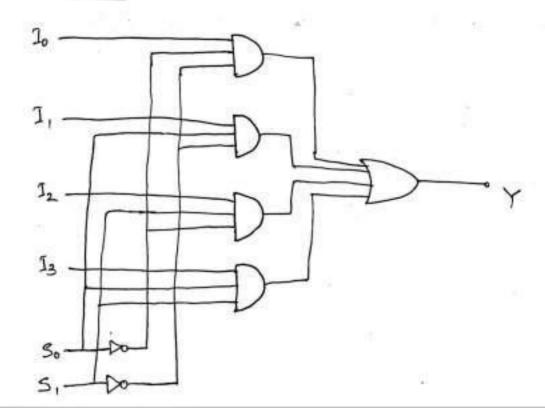

# 4 x 1 Multiplexer

- Each of the four inputs  $I_0,I_1,I_2$  &  $I_3$  are applied to the input of MUX & logic levels applied to the selection lines  $S_0$  &  $S_1$ .

### Function Table

| S  | S2  | 4   |

|----|-----|-----|

| 0  | 0   | 1,  |

| 0  | : 1 | 1,  |

| 11 | 0   | 12_ |

| 11 | 1   | 13  |

$$Y = \overline{S_1} \overline{S_0} I_0 + \overline{S_1} S_0 I_1 + S_1 \overline{S_0} I_2 + S_1 S_0 I_3$$

### Logic circuit

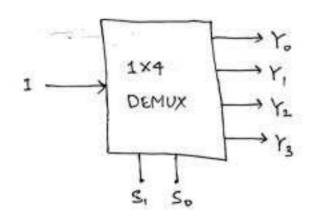

# Demuliplexer (DENUX)

- A demultiplexere is a combinational circuit that receives information on a Single line & transmits this on one of 2<sup>n</sup> possible output lines.

- The selection of a specific output line is controlled by the bit values of n selection lines.

- Demultiplexere is also known as data distributor, servial to parallel converter, one to many circuit.

- It is wed to pereform the neverse operation of MUX.

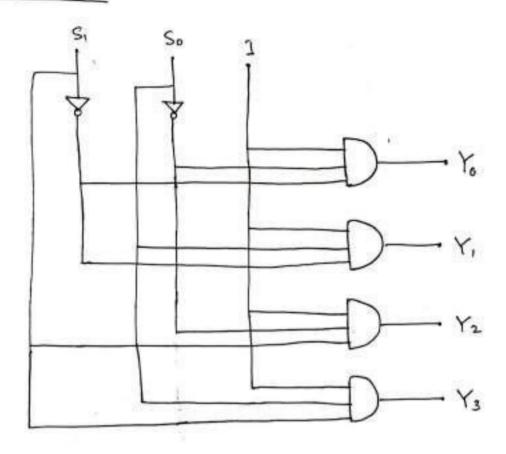

# 1×9 Demux

Two selection lines so & S, enable only one gate at a time of the data appearing on the input line will pass through the selected gate to the associated output line.

#### function table

| S, | So | Y3 | Y2 | ٧, | Yo |

|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 1  |

| 0  | 1  | 0  | 0  | 1  | 0  |

| ı  | 0  | 0  | I  | 0  | 0  |

| 1  | 1  | I  | 0  | 0  | 0  |

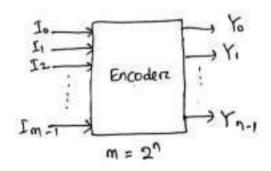

### Encodera

- It has 2° input lines & n output lines.

- out of 2° input lines only one is activated at a given time & produces an n-bit output code, depending upon which input is activated.

Encoder is used to convert other codes to binarry

- 1. octal to binary encoder (8x3 line)

- 2. Decimal to BCD encoder (10x4 line)

- 3. Hexadecimal to binary encoder (16x4 Line)

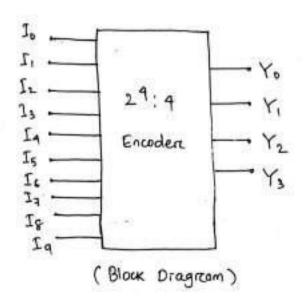

# Decimal to BCD Encoder

-It has ten inputs (0 to 9), & four outputs connexponding to BCD codes.

#### Trouth Table

| L9   | 18 | 14 | 16 | 15 | I4 | Î,    | $\Gamma_2$ | I, | 10 | Ya    | Y2 | Υ, | Y   |

|------|----|----|----|----|----|-------|------------|----|----|-------|----|----|-----|

| 0    | 0  | O  | 0  | 0  | 0  | 0.000 | 0          | _  | 1  | 10.00 | 0  | 0  | 0   |

| D    | O  | 0  | 0  | 0  | 0  | O     | 0          | t  | 0  | 0     | 0  | 0  | 1   |

| 0    | 0  | 0  | 0  | 0  | 0  | 0     | 1          | 0  | 0  | 0     | 0  | 1  | D   |

| D    | 0  | 0  | 0  | 0  | 0  | 1     | 0          | 0  | 0  | 0     | 0  | 1  | 1 - |

| 0    | 0  | 0  | 0  | 0  | 1  | 0     | 0          | 0  | 0  | 0     | 1  | 0  | 0   |

| 0    | 0  | 0  | 0  | V  | 0  | 0     | 0          | 0  | b  | 0     | 1  | 0  | 1   |

| 1320 | 0  |    |    | 0  | 0  | 0     | 0          | 0  | 0  | 0     | t  | 1  | 0   |

| 0    | 0  |    |    | 0  |    | D     | 0          | 0  | 0  | 0     | 1  | 1  | 1   |

| 0    | ı  | 0  |    | 0  |    |       | 0          | 0  | 0  | 1     | 0  | 0  | D   |

| 1    | 0  |    |    |    |    | 0     | 0          | 0  | 0  | 1,    | 0  | 0  | 1   |

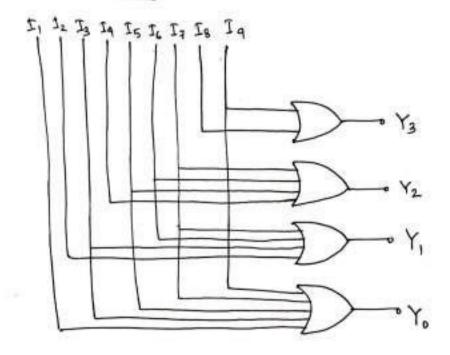

$$Y_0 = I_1 + I_2 + I_5 + I_7 + I_9$$

$Y_1 = I_2 + I_3 + I_6 + I_7$

$Y_2 = I_4 + I_5 + I_6 + I_7$

$Y_3 = I_8 + I_9$

### logic Diagram

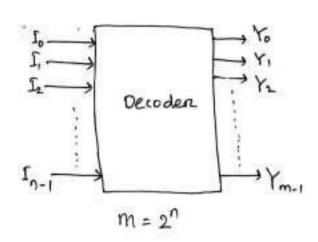

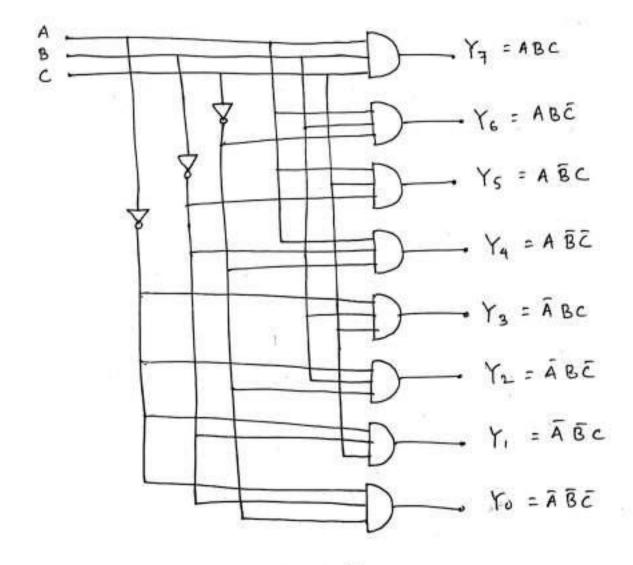

### Decoder

- It is a combinational logic circuit that converts binary information from 'n' bit input lines to a maximum 2" unique output lines only one output line is activated for each one of possible combinations of input.

- Decoders are wed to convert !-

- 1. Binary to octal (3×8 decoder)

- 2. Binary to Hexadecimal (4×16 decoder)

- 3. BCD to decimal (4x10 decoder)

### Truth Table

| A | В | C | Yo | Yı | Y2 | Y3 | Yq | Y5 | Y6 | Y 7 |

|---|---|---|----|----|----|----|----|----|----|-----|

| 0 | 0 | 0 | 1  | 0  | o  | 0  | O  | O  | 0  | D   |

| 0 | 0 | 1 | 0  | t  | D  | 0  | 0  | 0  | 0  | 0   |

| 0 | 1 | 0 | 0  | 0  | 1  | O  | 0  | 0  | 0  | 0   |

| 0 | 1 | 1 | 0  | 0  | 0  | 1  | 0  | 0  | D  | D   |

| 1 | 0 | 0 | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0   |

| t | 0 | 1 | 10 | 0  | 0  | 0  | 0  | 1  | 0  | 0   |

| 1 | 1 | 0 | 0  | 0  | 0  | 0  | O  | 0  | t  | 0   |

| 1 | 1 | 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1   |

## Logic Diagram

(3x8 Decoder)

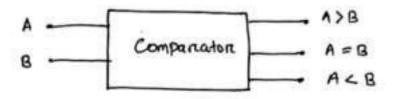

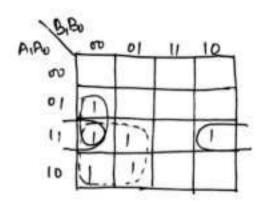

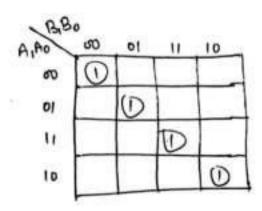

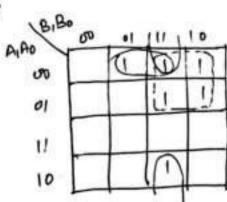

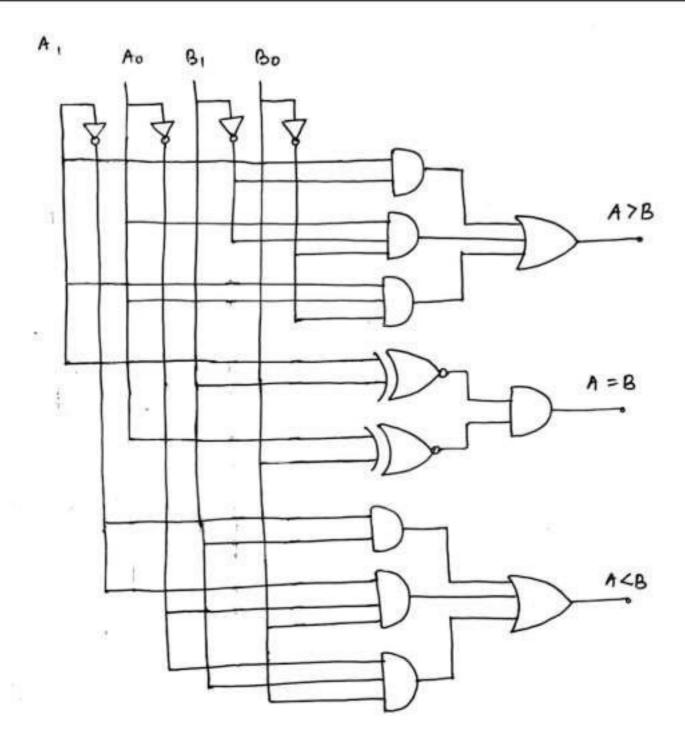

## 2-bit magnitude comparator

- A comparator used to compare two binarry numbers, each of two bits is called a 2-bit magnitude comparator.

- It consists of four inputs & three outputs to generate less than, equal to, & greater than between two binary numbers.

### Trent Table

|    | Input | 8  |    |     | output |     |

|----|-------|----|----|-----|--------|-----|

| A, | Ao    | В, | Bo | AKE | A=B    | A>8 |

| 0  | 0     | D  | D  | 0   | 1      | 0   |

| 0  | 0     | D  | 1  | 1   | 0      | 0   |

| 0  | 0     | 1  | O  | 1   | D      | 0   |

| 0  | 0     | 1  | t  | 1   | 0      | D   |

| 0  | ı     | 0  | O  | 0   | 0      | 1   |

| 0  | 1     | 0  | 1  | 0   | 1      | 0   |

| 0  | 1     | ı  | 0  | 1   | 0      | 0   |

| 0  | ι     | 1  | Ť  | T   | 0      | 0   |

| 1  | 0     | 0  | 0  | 0   | 0      | 1   |

| 1  | 0     | 0  | 1  | 0   | 0      | 1   |

| 1  | 0     | 1  | 0  | 0   | 1      | 0   |

| 1  | 0     | 1  | 1  | t   | 0      | 0   |

| 1  | 1     | 0  | 0  | O   | 0      | 1   |

| 1  | 1     | 0  | 1  | 0   | 0      | 1   |

| 1  | 1     | ı  | o  | 0   | 0      | 1   |

| 1  | 1     | 1  | 1  | O   | 1      | 0   |

A=B

ALB

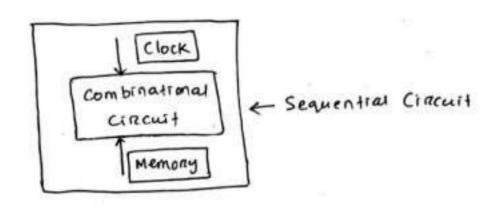

# Sequential Logic circuit

- In a sequential circuit, the output is dependent upon the present inputs as well as the past inputs of outputs.

- The sequential circuits include the memory elements, which store the past inputs & outputs.

- All the sequential circuits are clocked circuits that is all Sequential circuits work with a clock pulse.

- In Sequential circuit the owners is a function of the present inputs as well as the past inputs & outputs.

- In this memory is used to Store previous output & clock pulse decides the amount of time required to get the output.

# Difference between combinational & Sequential circuit

# Combinational Circuits

- outputs depend only on present inputs.

- Memory elements are not required.

- clock signal is not required.

- Feedback poth is not present.

- combinational circuits are faster.

- They are easy to design.

# Sequential crecuits

- Outputs depend on both present inputs and present.

- Memony elements are required.

- Clock signal is nequined.

- Feedback path is present.

- Sequential circuits are sowers.

- They are difficult to design.

The sequential circuits are classified as synchronous sequential circuits & a Synchronous sequential circuits depending on the timing of their signals.

# Synchronous Sequential circuit

- The change in input signals can affect memony element upon activation of clock signals.

- The maximum operational Speed of clock depends on time delays involved.

- In this circuit, memory elements are 'clocked flip-flops'.

- It is easier to design.

- It is generally 'edge traiggened'.

# Asynchronous Sequential Circuit

- The change in input signals can affect memony element at any instant of time.

- Because of absence of clock, this create can operate faster than Synchronous circuit.

- In this circuit, memory elements are either unclocked flip flops or time delay elements.

- More difficult to design .

- It is generally level triggened.

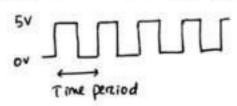

#### Clock Signal

clock Signal is a perciodic Signal & its on time & OFF time need not be the Same. We can respressent the clock signal as a square wave, when both its on time & OFF time are Same.

· In this case, the time period will be equal to either twice of on time on twice of OPF time.

- · The reciprocal of the time period of clock signal is known at the frequency of the clock signal .

- All the sequential circuits are operated with clock signal. So, the frequency at which the sequentral circuits can be operated accordingly the clock signal frequency has to be chosen.

# Types of Traiggering

- level thiggering

- · Edge traiggering

# Level targgering

There are two levels, namely logic high & logic low in clock Signal following are the two types of level traggering.

- positive level traggering

- Negative level traggering

positive level traggering: If the sequentral circuit is operated with the clock signal when it is in logic high, then that type of traggering is known as positive level traggering.

Negative level traggering: - If the sequentral circuit is operated with the clock signal when it is in logic low, then that type of traggering is known as negative level traggering.

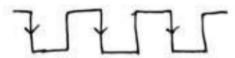

# Edge triggering

There are two types of transitions that occur in the clock signal. That means, the clock signal transitions either from logic low to logic high (or) logic high to logic low.

- . There are two types of edge trziggering based on the transitions of clock signal.

- positive edge tranggering

- Negative edge traggering

Positive edge traggering: If the sequential circuit is operated with the clock signal that is transitioning from logic low to logic high, then that type of traggering is known as positive edge traggering. It is also called as raising edge traggering.

# J J J J J

Negative edge tranggering: If the sequential circuit is operated with the clock signal that is transitioning from logic high to logic low, then that type of tranggering is known as negative edge tranggering. It is also called as falling edge tranggering.

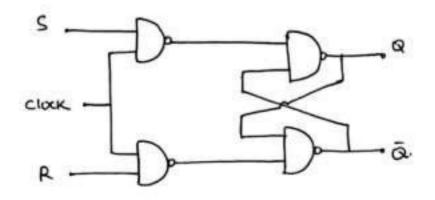

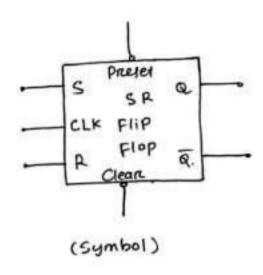

#### S-R Flip-Flop

#### Truth Table

| clock | S | P | Qnti | State   |

|-------|---|---|------|---------|

| 0     | × | × | Qn   |         |

| 1     | 0 | 0 | Qn   | Hold    |

| 1     | 0 | 1 | 0    | Reset   |

| 1     | 1 | 0 | 1    | Set     |

| 1     | 1 | 1 | ×    | Invalid |

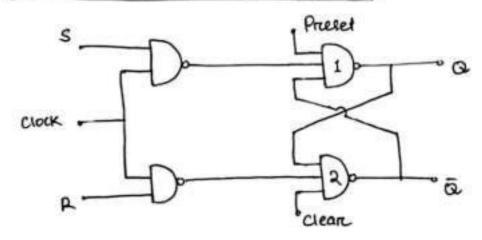

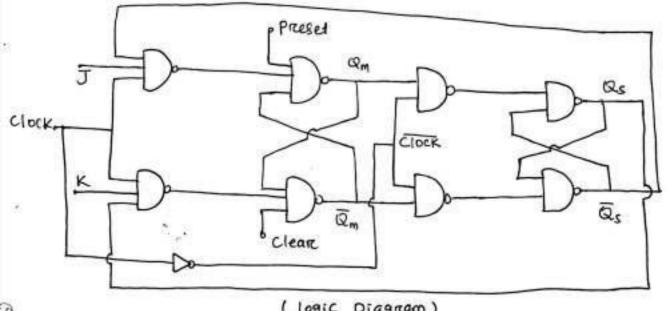

### clocked S-R Flip Flop with preset & clear .

- when presed = 0 & clear = 1, then the output of gated is 1 & that of Gate-2 is 0, which is independent of inputs S&R, and the flip-flop is Set.

- when preset=1 & clear=0, then the output of gate-2 is 1 which makes the output of chate-1 is 0 (i.e. Q=0), which is independent of inputs S&R, and the flip flop is reset.

- when preset=1 & clean=1, then outputs of Grate-1 & Grate-2 depend on other inputs. For normal operation, preset & clean are connected to logic 1.

- when present = 0 & clear = 0, then outputs of Gate-1 & Gate-2 tray to be come 1. Here, the uncertain State occurs & hence, present = 0 & clear = 0 is not used.

| Output  | Input |        |   |   |  |  |  |  |  |

|---------|-------|--------|---|---|--|--|--|--|--|

| Qnti    | Clear | Preset | R | S |  |  |  |  |  |

| 1       | 1     | 0      | × | × |  |  |  |  |  |

| 0       | 0     | 1      | × | × |  |  |  |  |  |

| On      | 1     | 1      | 0 | 0 |  |  |  |  |  |

| 0       | 1     | 1      | 1 | 0 |  |  |  |  |  |

| 1       | 1     | 1      | 0 | 1 |  |  |  |  |  |

| Invalid | 1     | 1      | 1 | 1 |  |  |  |  |  |

(No. Telephone Commission)

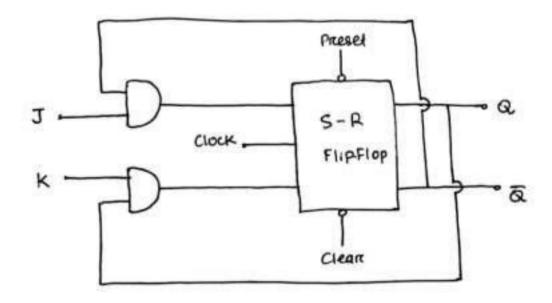

# JK flip flop using s.R flip-flop

- The uncertainty in the State of an S-R flipflop when S=R=1.

Can be eliminated by converting it into a J-K flip-flop.

| 11 | puts | out | outputs |   | s to SR | out put |

|----|------|-----|---------|---|---------|---------|

| 7  | K    | an  | ā,      | S | R       | Qnti    |

| 0  | 0    | 0   | ı       | 0 | 0       | 0 } 00  |

| 0  | 0    | 1   | o       | 0 | 0       | 1 7 00  |

| 1  | 0    | 0   | 1       | t | O       | 111     |

| ı  | 0    | ı   | 0       | 0 | 0       | 17.     |

| 0  | ı    | 0   | 1       | 0 | 0       | 040     |

| 0  | 1    | t   | 0       | 0 | ı       | 0 )     |

| 1  | 1    | 0   | ı       | 1 | 0       | 1 } @   |

| 1  | 1    | 1   | 0       | 0 | 1       | 0)~     |

### Truth Table of JK FlipFlop

| Clock | J | K | anti |            |

|-------|---|---|------|------------|

| O     | × | × | Qn   | -> memorzy |

| 1     | 0 | D | Qn   | -> Hold    |

| 1     | 0 | 1 | 0    | -) Reset   |

| t     | 1 | 0 | 1    | -> Set     |

| 1     | 1 | 1 | Q,   | -) Toggle  |

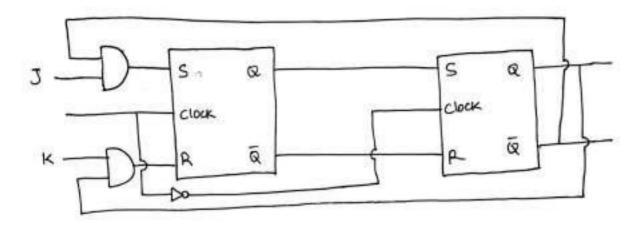

#### Race Around Condition

- If output at the FlipFlop is toggled more than once for one clock completion then it is known as Race around condition ore Racing.

- SR & D Flip Flops are free from reare condition.

- Edge triggering is also free from reare condition.

- Race condition may be occurred only in level triggering JK or T-Flip Plops.

- To avoid reace condition, there are two methods :-

- O to maintain tow < tod (FF) < T

- 1) Master Slave J. K Flip App

T - time period, tow-pulse width ]

tpd(ff) - Propagation delay of Ff

- The output of second S-R Flipflop is given to the input of the first Sa flip-flop through AND gale.

- The clock is directly applied to the first S-R Flip Flop after the NOT is applied to the second SR. Flip Flop.

- when clock=1, the first Flip Flop is enabled & the second flip Flop is disabled.

- Since the second Flip Flop is draabled, the output cannot be changed during the clock, which is the input fore the firest flipflop. Hence inputs are not changed during the clock of the problem of reace-around condition is resolved.

- . When clock =0, the first flip Flop is disabled & the second Flip-flop is enabled. The output of first flip-flop is the input fore the Second Flip-Flop.

- The first firp flop is known as master & the second is known as Slave.

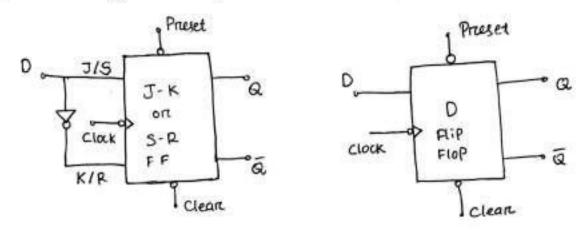

## D - FITP Flop

It has only one input referred to as D-input on data input.

### Trenth Table

| Clock | D | Qnti |

|-------|---|------|

| 0     | × | Rn   |

| 1     | 0 | 0    |

| 1     | 1 | 1    |

The input data appears at the output at the end of the clock pulse.

Thus the transfer of data from the input to the output is delayed

8 hence the name delay (D) Flip Flop.

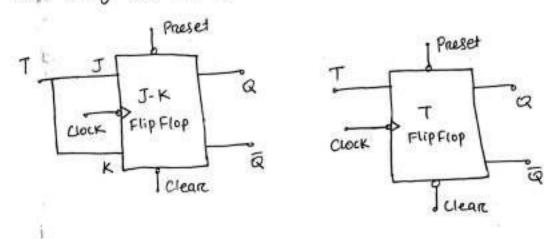

### T-Flip Flop

- In a J-K Flip Flop, if J=K, the nestling Flip Flop is referred to as a T-type Flip Flop.

- It has only one input, referred to as T-input.

### Truth Table

| Clock | Т | ant |  |  |

|-------|---|-----|--|--|

| 0     | × | Q,  |  |  |

| 1     | 0 | Qn  |  |  |

| 1     | 1 | Qn  |  |  |

- The designation T comes from the ability of the flip flop to Toggle on change state.

### Applications of FUP-FLOPS

- 3 Servial & parrellel data storage

- @ Data transfer

- (11) Servial to parallel conventer

- (ii) parrallel to servial converter

- (V) Laten

- (vi) counters

- (VI) Frequency division

# Modulus of a counter

- modulus counter on simply mod counter ance defined based on the number of states that the counter will sequence through before returning back to its original value.

- ex-a 2-bit counter that counts from ool to 112 in brancy has a modulus value of 4 (00 → 01 → 10 → 11) . Therefore it is called a modulo -9 on mod-4 counter.

- Mod-K up counter can count K number of states from 0 to K-1.

# difference between Synchronous counter & Asynchronous counters

### Synchronous Counter

- j. All the flipflops are triggened simultaneously with the Same clock.

- 2. Operation is faster.

- g. Any required Sequence can be designed.

- a Designing is complex as the number of States increases.

- 5 ex- Ring counter, Johnson counter

# Asynchronous counter

- 1. Different FlipFlops and traggered with different clock.

- 2. Operation is slower.

- 3. Will operate only in a fixed count sequence.

- q. Designing is easy even for more number of States.

- 5 · ex- Ripple UP counter, Ripple Down counter.

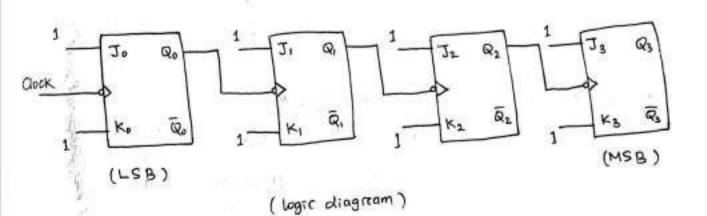

### 4-bit Asynchronous Counter

- It consists of a series connection of complementing J-K flip-flops, with the output of each flipflop connected to the clock pulse input of the next higher order flipflop.

- The flip flop holding the LSB receives the incoming clock pulses.

#### Operation

- There negative edge transgering is applied. So Flip Flops change their state on the negative going edge of clock pulse.

- 1 Note that all the flip flops are considered in toggled mode.

- (ii) Ro will change its state in every clock pulse.

- (i) Q, will change its State when Qo will change from 1 to 0.

- 10 Q3 will change its state when Q2 will change from 1 to 0.

### Tremh Table

| Clock | Q3  | Q2 | a,  | Q. |

|-------|-----|----|-----|----|

| 0     | 0   | 0  | 0   | 0  |

| 1     | 0   | 0  | 0   |    |

| 2     | 0   | 0  | 1   | 0  |

| 3     | 0   | 0  | 1   | 1  |

| 4     | 0   | 1  | 0   | 0  |

| 5     | 0   | 1  | . 0 | 1  |

| 6     | 0   | t  | 1   | 0  |

| 7     | 0   | 1  | 1   | 1  |

| 8     | 1   | 0  | 0   | 0  |

| q     | 1   | 0  | 0   | 1  |

| 10    | i i | 0  | l   | 0  |

| 11    | 1   | 0  | 1   | f. |

| 12    | 1   | 1  | O   | 0  |

| 13    | 1   | .1 | 0   | 1  |

| 14    | 1   | 1  | 1   | 0  |

| 15    | Ü   | 1  | i.  | -1 |

- Initially all flip flops are Set to Zero.

- The maximum possible state = 2 = 16 (from 0 to 15)

- If the input clock frequency is of then the output frequency is \$116.

- It is a 4 bit up counter, which counts from 0 to 15.

- FOR 4 bit down counter, positive edge triggering is applied & clock is given from Q (or) negative edge triggering is applied & clock is given from Q.

- . Four bit down counter counts from 15 to 0.

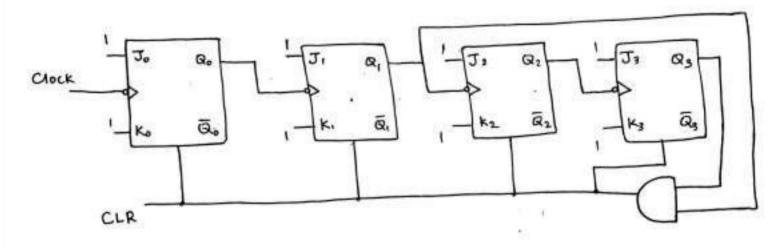

### Asynchronous Decade counter

- Herre the total numbers of flip flops required is 4, thus the numbers of used State = 10 & the numbers of unused State = 6.

- CLR is used to clear the flipflop i.e O.

- In order to design a non-binary decade counter a logic gove is used which detects to state from 0000 to 1001 & as soon as 1010 appears it clears all the flip-flops.

# Truth Table

|       |     | - 27 |    |    |

|-------|-----|------|----|----|

| Clock | Q3  | 02   | a, | ao |

| 0     | 0   | 0    | 0  | 0  |

| 1     | 0   | 0    | 0  | 1  |

| 2_    | 0   | 0    | Ţ  | 0  |

| 3     | D   | 0    | 1  | 1  |

| 4     | 0   | ı    | O  | D  |

| 5     | 0   | 1.   | 0  | 1  |

| 6     | 0   | 1    | ı  | 0  |

| Ŧ     | 0   | 1    | 1  | 1  |

| 8     | 1.0 | 0    | D  | 0  |

| 9     | 1   | 0    | 0  | 1  |

| 10    | 1   | O    | 1  | 0  |

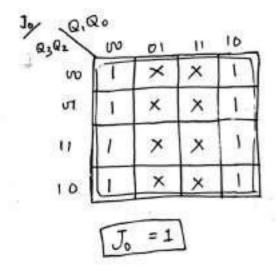

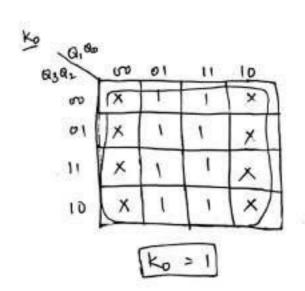

4-bit Synchronous Counter

- In Synchronous Counter all the flipflofs given clock Simultaneously.

| Present State Next Stal |    |    |     |         | tal 4 | Je Flip Flop Inputs |    |      |    |    |    |    |    |       |                |

|-------------------------|----|----|-----|---------|-------|---------------------|----|------|----|----|----|----|----|-------|----------------|

| Q3                      | Q, | a, | a.  | Q'a     | Q1    | Q,                  | a, | 3.   | K. | J, | K, | J, | K. | Ja    | K <sub>2</sub> |

| 0                       | 0  | 0  | 0   | 0       | 0     | 0                   | t  | 1    | x  | 0  | ×  | D  | ×  | 0     | ×              |

| 0                       | 0  | 0  | 1   | 0       | 0     | 1                   | 0  | ×    | 1  | 1  | X  | 0  | ×  | 0     | ×              |

| O                       | 0  | 1  | 0   | 0       | 0     | 1                   | 1  | 1    | ×  | ×  | 0  | O  | ×  | 0     | ×              |

| 0                       | 0  | 1  | 1   | 0       | 1     | 0                   | 0  | ×    | 1  | ×  | 1  | 1  | ×  | 0     | ×              |

| 0                       | 1  | 0  | 0   | 0       | 1     | 0                   | 1  | 1    | ×  | 0  | ×  | ×  | 0  | 0     | ×              |

| 0                       | 1  | 0  | 1   | 0       | 1     | 1                   | 0  | ×    | 1  | ı  | ×  | ×  | 0  | 0     | ×              |

| 0                       | 0  | 1  | 0   | 0       | 1     | 1                   | 1  | 1    | ×  | ×  | 0  | ×  | D  | 0     | ×              |

| 0                       | 1  | 1  | 1   | t       | 0     | 0                   | 0  | ×    | 1  | ×  | 1  | ×  | 1  | 1     | ×              |

| 1                       | D  | 0  | 0   | 1       | 0     | 0                   | -1 | J.   | ×  | 0  | ×  | 0  | ×  | ×     | 0              |

| i                       | 0  | 0  | 1   | t       | 0     | 1                   | 0  | ×    | 4  | 1  | ×  | 0  | ×  | ×     | 0              |

| 105                     | 0  | 1  | 0   | 1       | 0     | 1                   | 1  | 1    | X  | ×  | 0  | 0  | ×  | ×     | 0              |

| 1                       | 0  | 1  | 1   | . 1     | 1     | 0                   | 0  | ×    | 3  | ×  | 1  | 1  | ×  | ×     | 0              |

| 3                       |    | 0  | 0   | 1       | 1     | 0                   | 1  | 1    | ×  | 0  | ×  | ×  | 0  | X     | 0              |

| 31<br>27                | 9  | D  | ı   | 1       | 1     | 1                   | 0  | ×    | 1  | 1  | ×  | ×  | 0  | ×     | 0              |

| il.                     | ı  |    | 0   | ı       | 1     | 1                   | 1  | 1    | ×  | ×  | 0  | ×  | 0  | ×     | 0              |

| 1                       | 1  | 1  | 500 | 9.50    | 0     | 0                   | 0  | ×    | 1  | ×  | 1  | ×  | 1  | CARCO | 1              |

| 1                       | 1  | 1  | 1   | 0       | 0     |                     | _  | VC58 | 60 | 1  | =  | ^  | 1  | ×     | 1              |

| 0                       | 0  | 0  | 0   | met lib |       |                     |    |      |    |    |    |    |    |       |                |

# Registens

- A register is a digital circuit with two basic functions i.e. data storage a data movement.

- It is basically a group of Plip-flops Logically connected to perform various functions.

- To store a group of N-bit world, the numbers of flip-flops required is N (one for each bit).

- A register is a group of binary Storage cells suitable for holding binarry information. In addition to the firp-flops, a register may have combinational gates that perform certain data processing tasks. Thus a register consists of a group of flip-flops & gates that effect their transition.

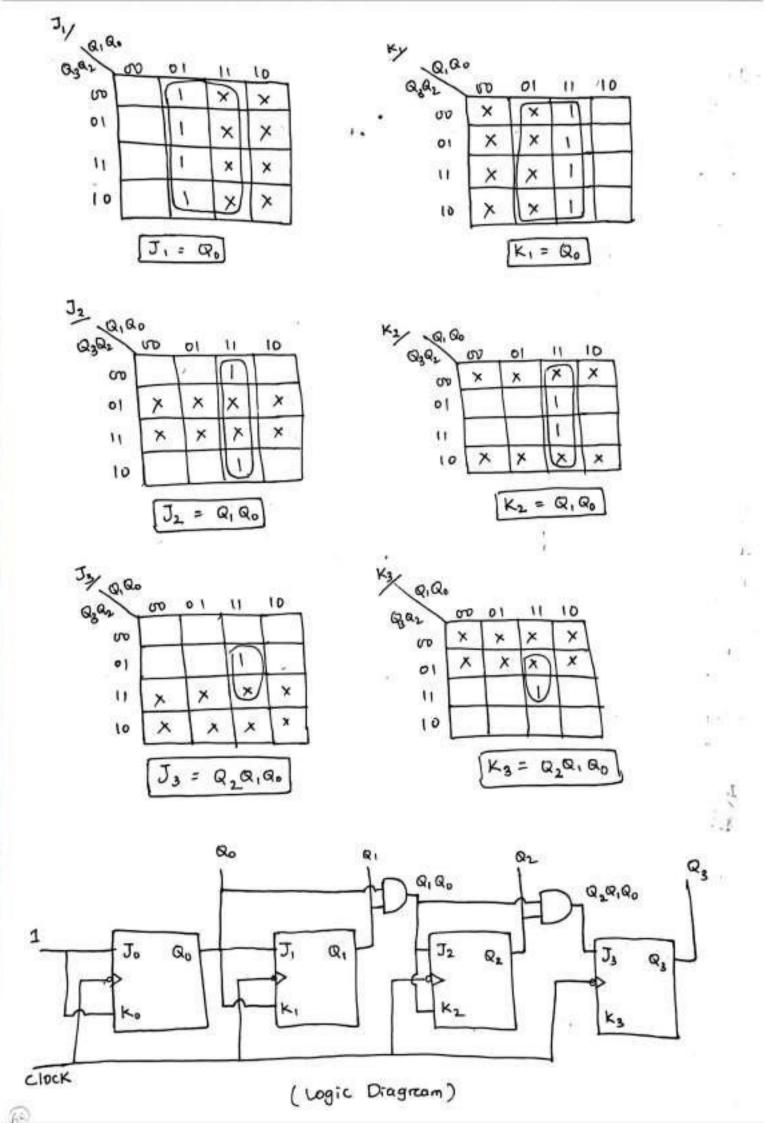

#### Shift Register

- A register capable of shifting the binary information entered into it from an external binary source is called the shift register.

- It is a sequential circuit mainly used to store or shift binary data either to the right on to the 1294.

- All flipflops receive a common clock pulse which causes shift from one State to the next.

- In snift register each clockpulse snifts the contents of register one bit position to the reight or left.

# Classification of shift Registers

- 1 Serial IN, Serial OUT shift register (SISO)

- 1 Serial IN, Panallel OUT Shift register (SIPO)

- @ Parallel IN, Sertial OUT Shift register (PISO)

- (v) parallel IN , Parallel out Shift register (PIPO)

IN - Input OUT - Output

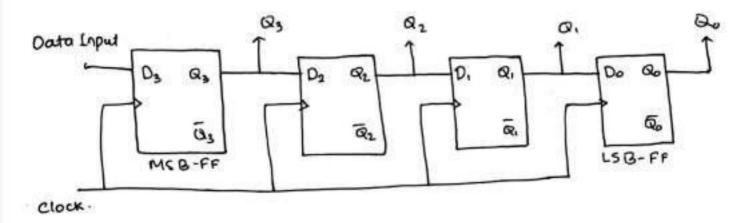

# ( Senial IN Senial out shift negister (SISO)

- The serial IN Serial OUT shift register accepts the data serially, one bit at a time on a single input line. It produces the stored binary information on its single output line in serial form.

- Let the binary information 1101 is applied to the input.

- Since shift register is reset, so initially all the flip-flop outputs are zero ine 0000.

- Data 1101 is applied to the input line. Therefore in the right Shift SISO register, LSB data is applied at the MSB FF (Dz).

| 8.0  | Q3    | Q2    | Q,         | a. | Clock |

|------|-------|-------|------------|----|-------|

| Data | 0.    | 0     | 0          | 0  | 0     |

| THE  | ١ د   | >0    | JO.        | OK | 1     |

|      | , o d | ١ ح   | 30         | 00 | 2     |

|      | л I.  | \ o . | ١. ٢       | 30 | 3     |

|      | 1     | > 1   | <b>)</b> 0 | 1  | 4     |

- In 'n' bit register, to enter h' bit data, it requires h' clock pulses in servial form.

- If h' bit data is storred in SISO register then output is taken serially, for this it requires (n-1) clock pulses.

- SISO register is used to provide a clock pulses delay to the input data.

# (i) Sercial IN Parallel OUT shift register (SIPO)

- In this shift register, data is entered in serial form but output is taken in parallel form. Therefore, once the data is storted each bit is available on its respective output lines simultaneously.

| Input | Data | 1101 | ٠ | Q3 | az | α, | 00 | CLOCK |              |

|-------|------|------|---|----|----|----|----|-------|--------------|

|       |      |      |   | 0  | D  | 0  | 0  | 0     | -> Initially |

|       |      |      |   | 1  | 0  | O  | 0  | 1     |              |

|       |      |      |   | 0  | 1  | 0  | 0  | 2     |              |

|       |      |      |   | 1  | 0  | ı  | 0  | 3     | 19           |

|       |      |      |   | 1  | 1  | 0  | 1  | 4     |              |

- for storing n-bit servial input data number of clock pulses required = n.

- For n-bit parallel output data to be storred the number of clock pulses required = 0.

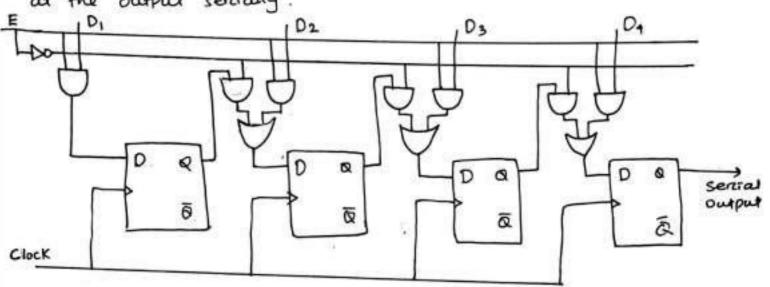

# (ii) Parallel IN Serial OUT Shift Register (PISO)

In PISO shift register the data bits are entered simultaneously into the respective flip flops and the shifted data is available at the output serially.

- when E is one input data is given as when E is zero output taken.

- To Stone parallel data of n-bit it requires I clock pulse . .

- To stone serial output data of n-bit the no. of clock puses required are (n-i).

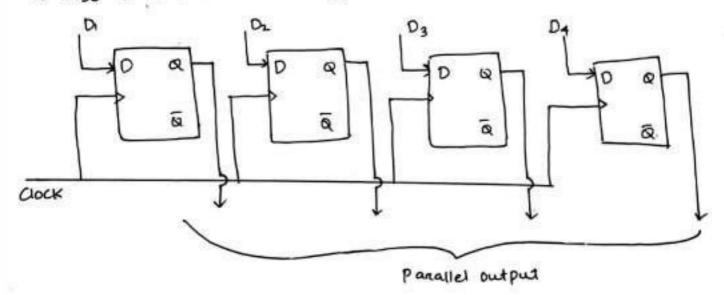

#### ( Parallel IN Parallel OUT shift negister (PIPO)

- In this register the input is a parallel entry of the output is also taken simultaneouty.

- For parallel IN data the number of clock pulse required is 1 - For parallel OUT data the number of clock pulse required is 0

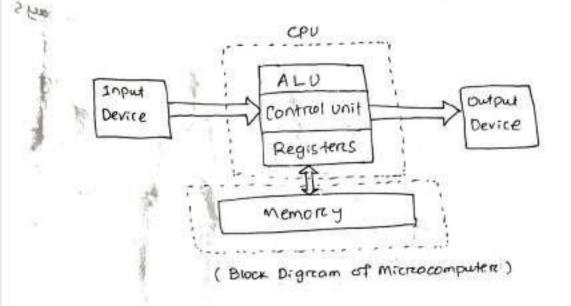

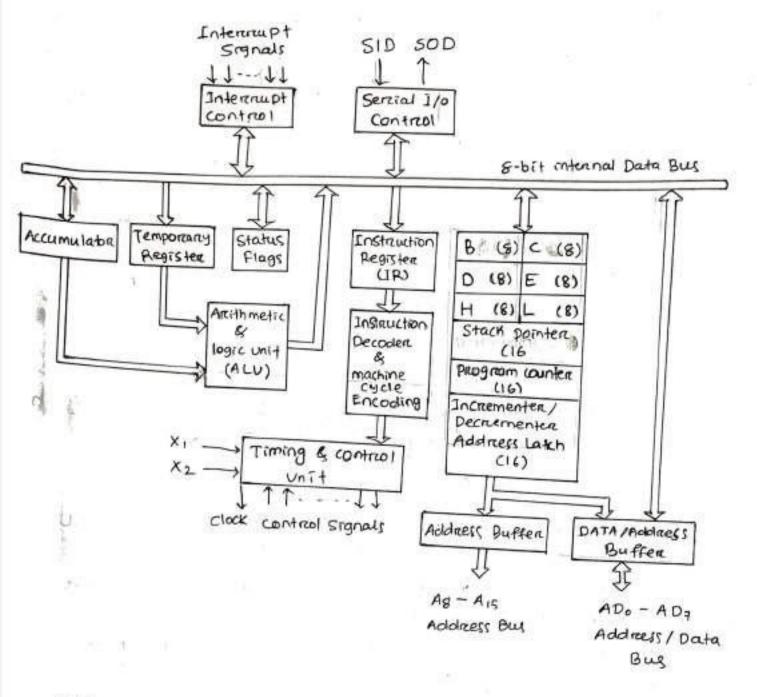

#### Microprocesson

Register based electronic device that reads binary instructions from memory, accepts binary data as input & processing this data according to the instructions written in the memory.

The microprocessor is capable of performing computing functions by making decisions to change the sequence of program execution. The microprocessor can be embedded in a larger system, & can

function as the CPU of a computer called a microcomputer.

- Input device is a device that transfers information from outside world to the computer example: Keyboard, mouse, microphone etc.

- The output device transfers information from computer to the outside world like monitor, printers, speaker, projector etc.

- . Memorey is an electronic medium that Stories binary information.

- CPU Crentral processing unit) is the heard of computer systems.

The microprocessor in any microcomputer acts as a CPU.

The CPU can be made up with ALU, CP, Registers.

- ALU is the group of circuits that pereforms arithmetic & logical operations.

- CU (control unit) is a group of circuits that provide timings g signals to all the operations in the computer & controls the data flow.

#### System Bus

A but is a group of wires/lines used to transfer dato between components inside a computer or between computers. They are communication path used to carry the signals between microprocessor & peripherals.

The system bus of a microprocessor is of 3 types

### 1 Address Bus

- It is a group of times that are used to send a memory address on a device address from the microprocessor unit (MPU) to the memory or the peripheral.

- The address but is always uni-directional i.e. address always goes out of the microprocessor.

- If the address lines are n for a MPU then its addressing capacity is 2n.

### 2 Data Bu

- It is group of lines used to transfer data between the microprocesson & peripherals and lon memory.

- Data but is always bi-directronal.

# 3 contreol Bus

- control 12m provides signals to control the flow of data.

#### ALU

The anithmetic & Logic unit, ALU, Penforms anithmetic & logical operations such as Addition, subtraction, logical AND, OR, XOR, NOT, increament, decrement, left shift, notate left, notate right, clear etc.

### Timing & Control unit

- The timing & control unit is a section of the CPU- It generally timing & control signals which are necessary for the execution of instructions.

- It controls data flow between CPU & peripherals.

- It controls the entire operations of the microprocessor & percipherals connected to it. Thus it is seen that the control unit of the CPU acts as the breain of the computer system.

#### Register

- Registers are used by the microprocessor for temporary storage 8 manipulation of data & instructions.

- 8085 microprocessor has the following registers:

- 1 one & bit accumulator i e Register A

- (i) Six 8-bit general puripose registers. These are B, C, D, E, H & L

- ( One 16-bit Stack pointer, SP

- @ one 16-bit preogram counter, PC

- 1 Instruction register

- 1 Temporary register

- 8085 microproversor also contains a set of five flipflops which serve as flags on status flags

#### Accumulator

50

- The accumulator is an 8-bit register associated with the ALU. The register A in the 8085 is an accumulator.

- It is used to hold one of the operands of an anithmetric on logical operation. It serves as one input to the ALU.

- The final result of an arithmetic or logical operation is placed in the accumulator.

#### General purpose Registers

- The 8085 microprocessor contains six 8-bit general-purpose registers. They are B.C.D.E.H & L register.

- To hold 16-bit data a combination of 2 8-bit registers can be employed. The combination of two 8-bit registers is known as a register-pair. The valid register pairs in the 8085 are B-C, D-E & H-L.

- The H-L pairs is used to act as memory pointer & for this purpose it holds the 16-bit address of a memory location.

## Program counter (PC)

- It is a 16-bit special purpose register. It is used to hold the memorry address of the next instruction to be executed.

- The micreoprocessor incree ents the content of the program counter during the execution of an instruction so that it points to the address of the next instruction in the program at the end of the execution of an instruction.

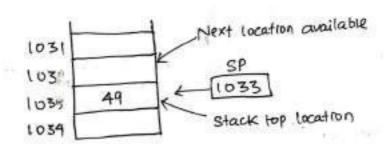

## Stack Pointer (SP)

- It is a 16-bit special purpose register. The stack is a sequence of memory locatrons set aside by a programmer to storce/retrieve the contents of accumulation, flags, program counter & general purpose registers during the execution of a program.

- The Stack pointer (SP) controls addressing of the Stack. The SP holds the address of the top element of data stored in the Stack.

#### Instruction Register

- The instruction register holds the operation code on instruction code of the instruction which is being decoded & executed.

## Temportary Register

- It is an 8-bit register associated with the ALV. It holds data during an anithmetic/logical operation.

- It is used by the microprocesson. It is not accessible to programmen.

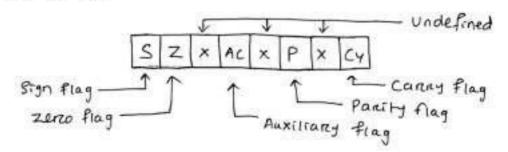

## Flags

- 8085 microprocessor contains five flipflops to se ve as status flag.

- 1 Carry Flag (C4)

- (P) Panity Flag (P)

- 3 Auxiliany conny Flag (AC)

- 1 Teno Flag (Z)

- 1 Sign Flag (S)

## ( Carry flag (CY)

- After the execution of an arithmetic instruction if a carry is produced, the carry flag cy is set to 1, otherwise it is 0.

- After the addition of two 8-bit numbers, if the Sum is larger than 8 bits, a carry is preoduced of the carry flag is sel to 1.

# 2 parity flag (P)

The partity flag p is set to 1, if the result of an artithmetic on logical operation contains even number of 1's. It is reset on 0, if the result contains odd number of 1's.

# 3 Auxiliany Conny Flag (AC)

- The auxiliary carry flag holds carry out of the bit number 4 to the bit number 5 resulting from the execution of an arithmetic operation.

#### (3) zeno Flag (Z)

The zero Statu flag z is set to 1, if the result of an anithmetic on logical operation is 0. If the result is not zero, the flag is set to 0.

## (5) Sign flag (S)

The sign flag S is set to 1, if the nesult of an anithmetic on logical operation is 0. If the nesult is positive, the sign flag is set to 0.

$$\begin{array}{c} C8 \to 0^{5} \\ 11001011 \\ E9 \to 11101001 \\ \hline \hline 10110100 \end{array}$$

- Result is non zero; [Z = 0]

- MSB of the sum is 1; [S=1] i.e result is negative.

- There is a carry from 4th bit to 5th; [AC=1]

- There is a carry generated at the final bit or MSB; [CY=1]

- There are 4 no. of 1s; [P=1] (even no. of 1)

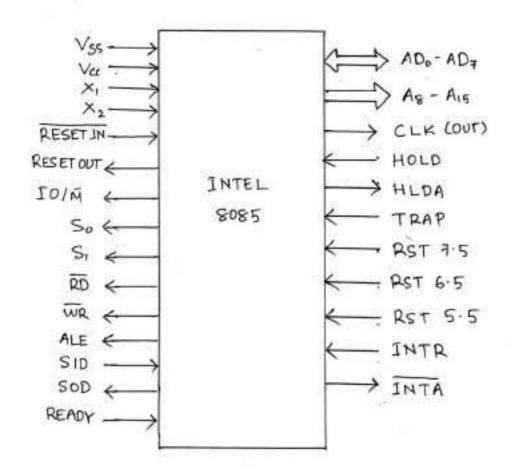

# Pin Diagram

## A8-A15

2

These are address bus & are used for the most significant bits of the memory address on 8-bits of 1/0 address.

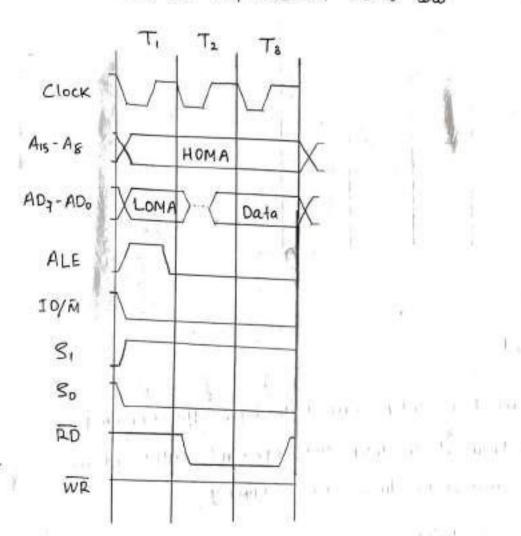

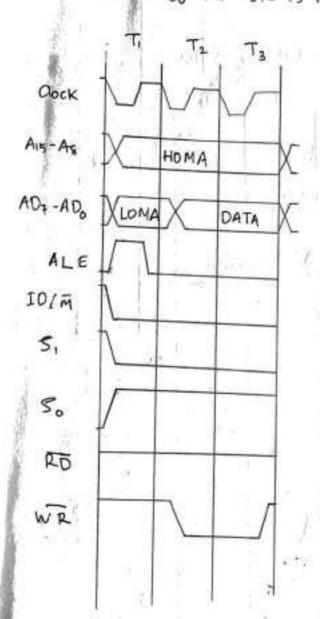

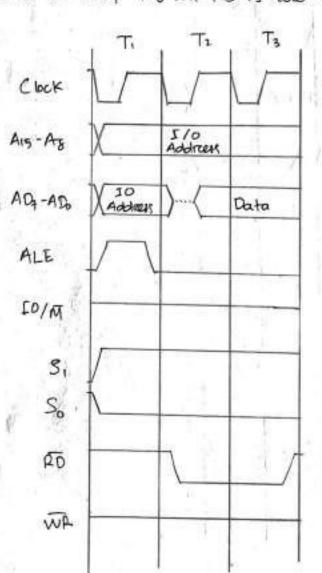

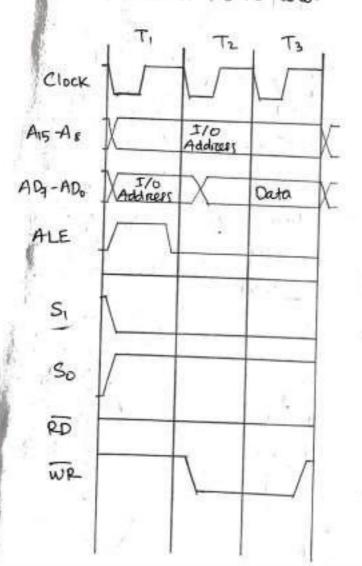

### ADo-AD7

These are time multiplexed address/data bus i.e they serve dual purpose. They are used for the least significant 8-bits of the memory address on 1/0 address during the first clock cycle of a machine cycle. Again they are used for data during second & third clock cycles.

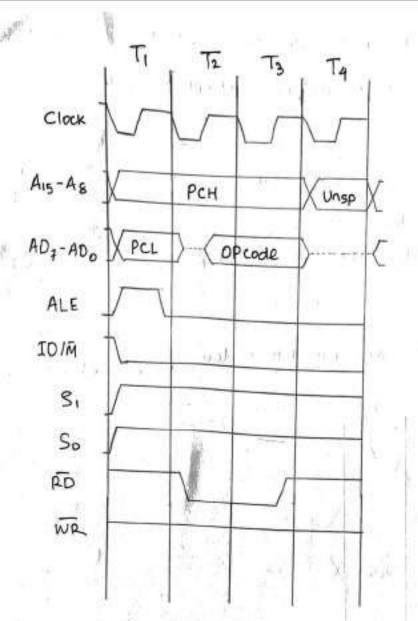

#### ALE (Address Later Enable)

· It is an address later enable signal. It goes high during first clock cycle of a machine cycle & enables the lower 8-bits of the address to be latched. It goes low for data operation.

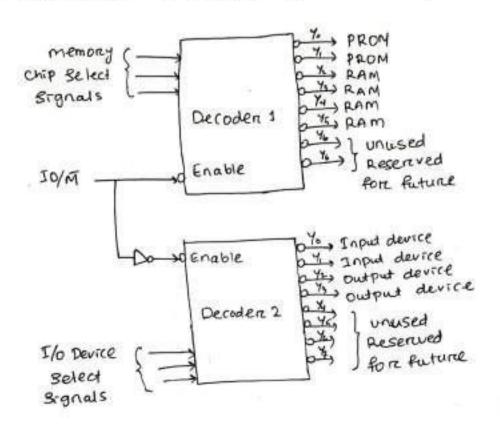

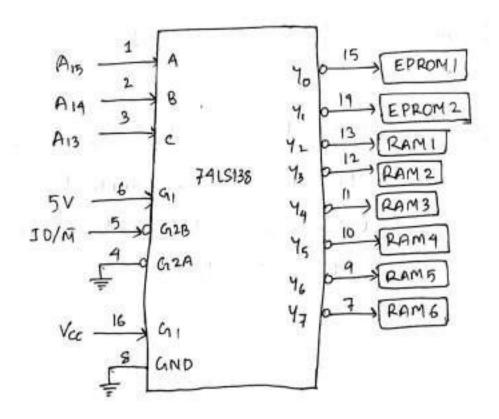

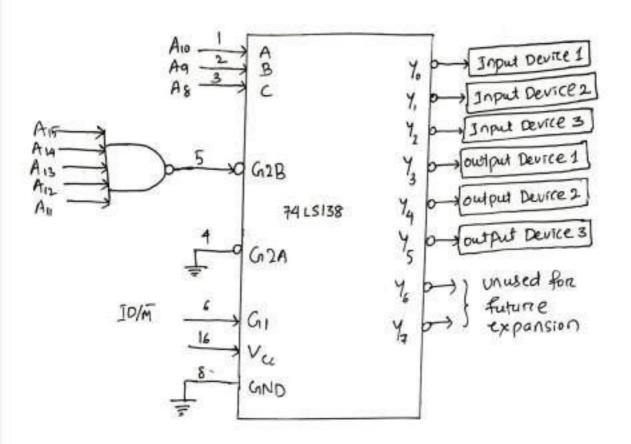

#### ID/M

- -It is a Status signal which distinguishes whether the address is for memory or 1/0.

- when it goes high, the address on the address bus is for an I/o device when it goes low, the address on the address bus is for a memory location.

#### 50,51

These are status signals sent by the microprocessor to distinguish the vanious types of operation.

| So | operation |  |  |  |

|----|-----------|--|--|--|

| 0  | Halt      |  |  |  |

| 1  | write     |  |  |  |

| 0  | Read      |  |  |  |

| 1  | Fetch     |  |  |  |

|    | 1         |  |  |  |

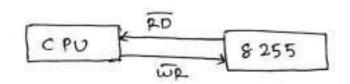

RD

when microprocessor reads data from a memory location on input device, it is called Read operation. RO is a signal sent by the microprocessor to the memory / input device to control Read operation when it goes low, the selected memory or input device is read.

when microprocessor sends data to a memory location on an output device, it is called write operation. WE is a signal sent by the microprocessor to the memory/output device to control write operation, when it goes low, the data which is on the data bus, is written into the selected memory on sent to the output device.

READY

- It is a signal sent by an input or output device to the microprocesson.

This signal indicates that the input or output device is ready to

Send on receive data.

- The microprocesson examines READY signal before it penforms data transfer operation. A Slow input on output device is connected to the microprocesson through READY line.

- when READY is high, it indicates that the input or output divice is ready to send on neceive data. When READY is Low, the microprocessor waits till READY becomes high. The microprocessor examines the status of READY signal in the second clock cycle of the machine cycle.

#### HOLD

- when another divice of the computer System, requires address of data buses for data transfer, it sends toold signal to the microprocessor. After receiving the Hold request, the microprocessor sends out a HLDA (HOLD Acknowledge) Signal to the device.

- Then the microprocessor leaves the control over the buses as soon as the current machine cycle is completed. The microprocessor regains the control over the buses after the HOLD signal is removed.

#### HLDA

- It is a HOLD acknowledge signal sent out by the microprocessore after receiving the HOLD Signal. It is sent to the device which has issued the HOLD signal. After the removal of the HOLD signal, the HLDA goes low, and thereafter the microprocessor takes over the buses.

(8)

#### INTR

- It is an interrupt signal sent by an external device to the microprocessore. Through this line an external device informs microprocessor that it is ready to transfer data one to initiate ceretain operation:

- The 8085 micropreocessor has 5 interrupt lines. The INTR is one of them when it goes high, the micropreocessor suspends the execution of its normal sequence of instructions after completing the current instruction at hand, it attends the interrupting device.

## INTA

It is an interrupt acknowledge Signal issued by the microproxessor after receiving an interrupt request from an external device. It is a low active Signal.

#### RST 5.5, 6.5, 7.5 & TRAP

These are interrrupts, when an interrrupt is recognised the next instruction is executed from a fixed location in the memory.

TRAP — 0024

RST 5.5 — 002C

RST 6.5 — 0034

RST 7.5 — 003C

- The TRAP has the highest precority among interrrupts - It is a nonmaskable interrupt .

#### RESET IN

It rejets the program counters to zero. It also neseds interrupt enable & HLDA flipflops. It does not affect any other flag or register except the instruction register. The CPU is held in neset condition as long as RESET is applied:

#### RESET OUT

It indicates that the CPU is being reget.

## X1.X2

These are terminals to be connected to an external crystal oscillator which drives an internal circuitry of the microprocessor to produce a Suitable clock for the operation of microprocessor.

#### CLK

It is a clock output for user, which can be used for other digital Ics.

Its frequency is some at which processor operates.

#### 510

It is data line for serial input. This pin is used for receiving the data into microprocessor serially.

#### SOD

It is a data line for Servial output. This pin is used for sending the data from the microprocessor servally.

4100

Vcc

+5 Volts supply

Vss

Conound reference

During the execution of a program sometimes it becomes necessary to save the contents of ceretain registers because the registers are required for some other operation.

- These contents are moved to certain memory weatrons by PUSH operation. After completing the operations those contents which were saved in the memory are transferred back to the registers by POP operation.

- The memory locations kept for this purpose is called stack.

Stack top: The last memory location of the occupied portion of the occupied portion

Stack pointer: - A special purpose 16-bit register known as stack pointer holds the address of Stacktop.

- Data are Storred in the stack on last-in-firest-out (LIFO) preinciple.

- Push To add an element to the stack.

- Pop To remove an element from the Stack.

# Interrupt

Which are requesting its services, it stops its current execution is program control is transferred to a sub-routine by generating CALL signal & after executing sub-routine by generating RET Signal again program control is transferred to main program from where it had Stopped.

# Hattchware & Software interrupts

- When microprocessors receive interrupt signals through Pins of microprocessor, they are known as Hardware interrupts.

- There are 5 Handware interrupts in 8085 microprocessor. They are INTA, RST 7.5, RST 6.5, RST 5.5, TRAP.

- · software interrupts are those which are inserted in between the progream which means these are mnemonics of microprocessor.

- There are 8 software interrupts in 8085 microprocessor. They are RST 0, RST 1, RST 2, RST 3, RST 4, RST 5, RST 6, RST 7.

## vectored & Non-vectored interrupts

- · vectorced interrupts are those which have fixed vector address & after executing these, program control is transferred to that address.

- . Non-vectored interrupts are those in which vector address is not predefined. The interrupting device gives the address of sub-routine for these interrupts.

- INTR is the only non-vectored interrupt is 8085 microprocessor.

### maskable & non maskable Interrrupts

maskable interrupts are those which can be disabled on ignored by the microprocessor. These interrupts are either edge-thinggered on level-thinggered, so they can be disabled.

- INTR, RST 7.5, RST 6.5, RST 5.5 are maskable interrupts in 8085 microprocessor.

- Non maskable interrupts are those which can not be disable or ignored by microprocessor.

- TRAP is a non-markable interrupt. It consists of both level as well as edge triggering.

- 3 if the efficient beeth is the court our many a court of the

the R. M. Tage he would be the received absorbed by the first state of the

and the second of the second o

the condition was the condition of the c

the crosses it. Exposes these dissections are not been award

William In Comment of the Comment

respective from the control page 1000 person you

### Presonity of Internapts

TRAP Highest

RST 7.5

RST 6.5

RST 5.5

INTR Lowest

### OPcode & operand.

Each instruction contains two parets: operation code copcode) & operand.

opcode! The first part of an instruction which specifies the task to be performed by the computers is called opcode.

operand: The second part of the instruction is the data to be operated on, and it is called operand.

- The operand given in the instruction may be in various forms such as 8-bit one 16-bit data, 8-bit one 16-bit address, internal registeres one a register on memory location.

- In some instructions the operand is implicit.

- when operand is a register it is underestood that the data is the content of the register.

#### Instruction world size

According to the world Size the inte 8085 instructions are classified into 3 types:

Brown the residence for the

white of received and in the term of the

magneto e Tor

- 1 Byle instruction

- 2 2-Byte instruction

- 3 3-Byte instruction

#### 1 one-Byte instruction

4 1-Byte instruction includes the opcode of the operand in the same Byte.

### ex MOV A, B

- copy the content of the B register in Accumulator.

ADD B

- Add the content of register B to the content of the accumulator.

- Invert on complement each bit in the accumulator

- 1 Two Byte instruction

- In a two-byte instruction the 1st byte of the instruction is its opcode & the 2nd byte 15 either data on additess. the state of the s

ex

MVI B, 05

move data of to negister B IN OI

Note that the property will be the control of the c Accept data byte from an input device & place it in the accumulator.

garage and the State Contractor

continued to the author

- 3) Three Byte instruction

- In a three byte instruction the 1st byte of the instruction is its opcode & the 2nd & 3nd bytes are either 16-bit data on 16-bit addness.

👺 in the Market in the property of the first of the All the A

LXI H, 2400H

Load H-L pair with 2900H

LDA 2500H

Cret the Content of the memory location 2500H into accumulatore.

spanicionimical and sectionally in the government and regard ...

and absolute and the first transfer of the contract of the contract of

the formula of the continuous and the continuous continuous accounts a continuous and the continuous and the

and other transaction of the property of the part of t

# Instruction set of 8085

## Data Transfer

MOV RITEZ

- move content of 12 register to 12, register.

MOV A, B [contents of register B moves to register A]

- 1 Byte instruction.

Mov R, M

· Move content of memory to register it.

- The content of the memorry location, whose additess is in H-L pair, is moved to register it.

If a self-se will like the second activities the second

- 1-Byte instruction.

## n. Mov m, R

- move the content of register to memory.

= Mov m, c [moves content of register c to the memory location whose address is in H-L pair.]

## MVI n, data

- move immediate data to register.

- It is a 2-Byte instruction. 1st Byte is opcode, 2nd Byte is data.

- MVI A, 15 [data 15 moves to negisten A)

# MVJ M, data

- -move immediate data to memory

- 2 Byte instruction.

MVI M. 50 [move 50 to memory location whose address it in the pairs]

# LXI TP, data 16 bit

- Load 16-bit immediate data into register pair rep.

- If LXIH is mentioned, it denotes HL pairs.

5x

LXI H, 2050H [I+ loads 2050 into HL pair

- It is a 3-Byte instruction. 1st Byte is LXIH, and Byte is 20 & 3rd Byte is 50.

#### LDA address

The content of the memory location specified in the instruction is loaded into the accumulator.

EX LDA 3020H [content of 3020 moves to Accumulatore]

- It is a 3 Byte instruction

# STA address

The content of the accumulator is stored in the memory weation specified in the instruction.

STA 6523H [Content of accumulation Storce in 6523H]

- It is a 3 Byte instruction.

# LDAX RP

The content of the memory location, whose address is in the register pairs rep, is loaded into the accumulators.

LDAX B [wad the content of the memory weatron, whose address is in the B-c pair into the accumulator]

- It is a 1-Byte instruction.

# STAX RP